# INTRODUCTION OF 8085 MICROPROCESSOR

# CHAPTER OUTLINE

- Block diagram of a computer system

- Basic components of a computer system using block diagrams:

- o Cpu

- Memory

- Input and output unit

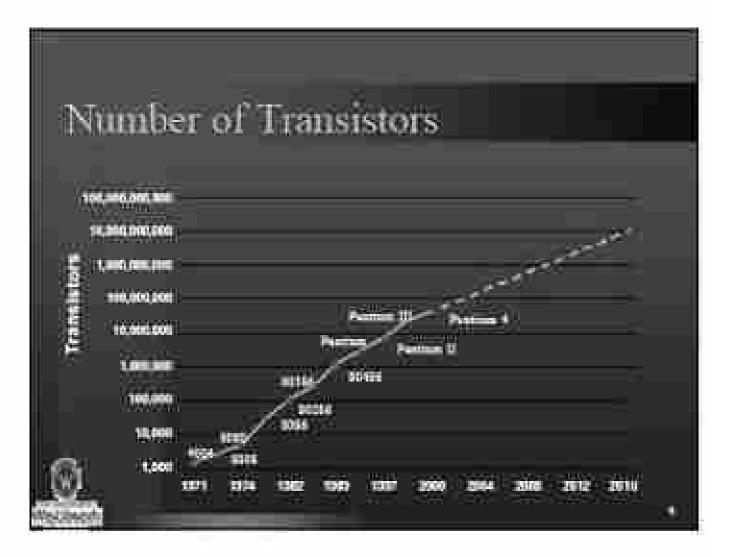

- Evolution of microprocessor: 4,8,16,32 dan 64 byte

- Nibble, byte, word dan longword

- Fecthing and execution cycles.

- Internal structure and basic operation of a microprocessor (arithmetic and logic unit, control unit, register sets, accumulator, condition code register, program counter, stack pointer)

- Bus system: data bus, address bus and control bus.

- Microprocessor clock system

- Examples of microprocessor: 8085,8086.

# Introduction

A computer is a programmable <u>machine</u> that receives input, stores and manipulates <u>data</u>//<u>information</u>, and provides output in a useful format.

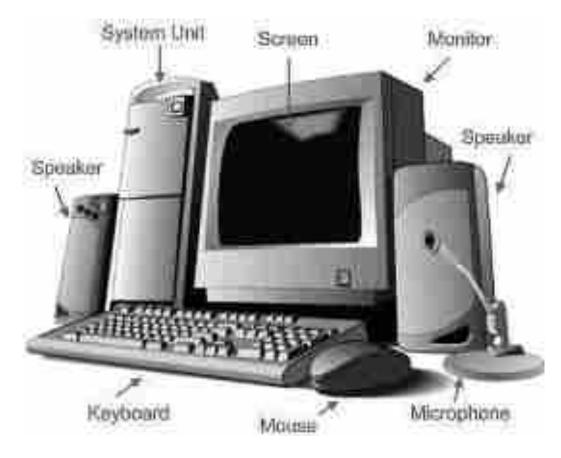

#### 1.1 DIAGRAM OF A COMPUTER SYSTEM A computer is a programmable <u>machine</u> that receives input, stores and manipulates <u>data//information</u>, and provides output in a useful format.

Diagram Of A Computer System

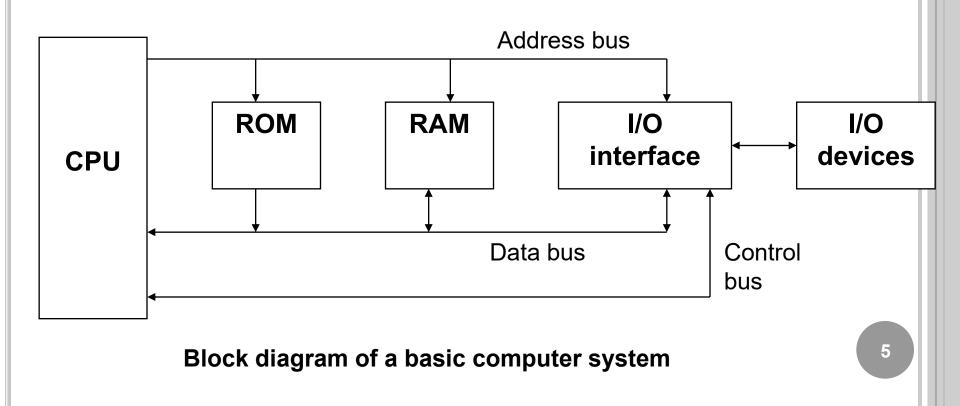

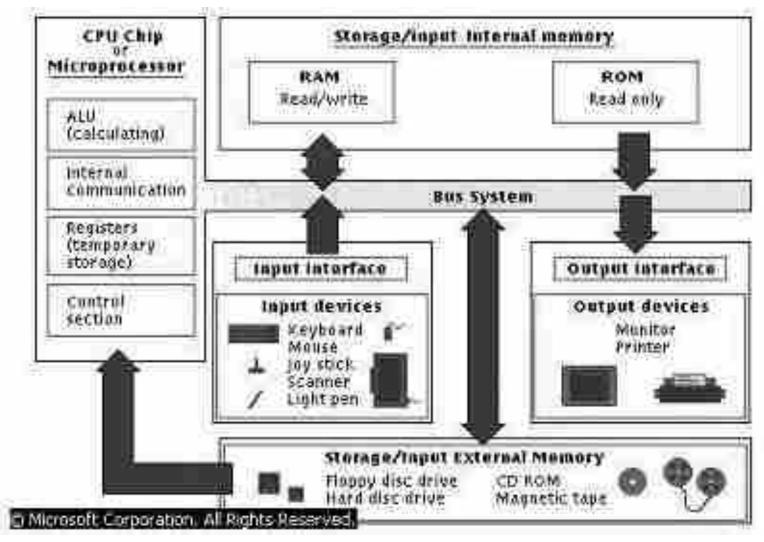

# 1.1 BLOCK DIAGRAM OF A BASIC COMPUTER SYSTEM

Basic computer system consist of a Central processing unit (CPU), memory (RAM and ROM), input/output (I/O) unit.

## BASIC COMPONENT OF MICROCOMPUTER

## 1. CPU - Central Processing Unit

- the portion of a computer system that carries out the instructions of a computer program

- the primary element carrying out the computer's functions. It is the unit that reads and executes program instructions.

- The data in the instruction tells the processor what to do.

Pentium D dual core processors

# 2. Memory

- physical devices used to store data or programs (sequences of instructions) on a temporary or permanent basis for use in an electronic digital computer.

- Computer main memory comes in two principal varieties: <u>random-access memory</u> (RAM) and <u>read-only memory</u> (ROM).

- RAM can be read and written to anytime the CPU commands it, but ROM is pre-loaded with data and software that never changes, so the CPU can only read from it.

- ROM is typically used to store the computer's initial start-up instructions.

- In general, the contents of RAM are erased when the power to the computer is turned off, but ROM retains its data indefinitely.

- In a PC, the ROM contains a specialized program called the <u>BIOS</u> that orchestrates loading the computer's <u>operating system</u> from the hard disk drive into RAM whenever the computer is turned on or reset.

# 3. I/O Unit

- Input/output (I/O), refers to the communication between an information processing system (such as a <u>computer</u>), and the outside world possibly a human, or another information processing system.

- <u>Inputs</u> are the signals or data received by the system, and <u>outputs</u> are the signals or data sent from it

- Devices that provide input or output to the computer are called peripherals

- On a typical <u>personal computer</u>, peripherals include input devices like the keyboard and <u>mouse</u>, and output devices such as the <u>display</u> and <u>printer</u>. <u>Hard disk drives</u>, <u>floppy disk drives</u> and <u>optical disc drives</u> serve as both input and output devices. <u>Computer networking</u> is another form of I/O.

# EVOLUTION OF MICROPROCESSOR

# DATA SIZE

| Nibble    | 4 bit  | Nibble = 4 bit (n = 0-3)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-----------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Byte      | 8 bit  | Byte = 0 pt (n = 0.0)<br>Hange 0 gsz<br>Fignals<br>Timple<br>Timple<br>Timple<br>Timple<br>Timple<br>Timple                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Word      | 16 bit | Word = 16 bit (n= 0.15)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Long word | 32 bit | Image: State of the s |

- 8-bit general purpose microprocessor

- Capable to address 64k of memory

- Forty pins, requires +5 V single power supply

- o 3-MHz single-phase clock.

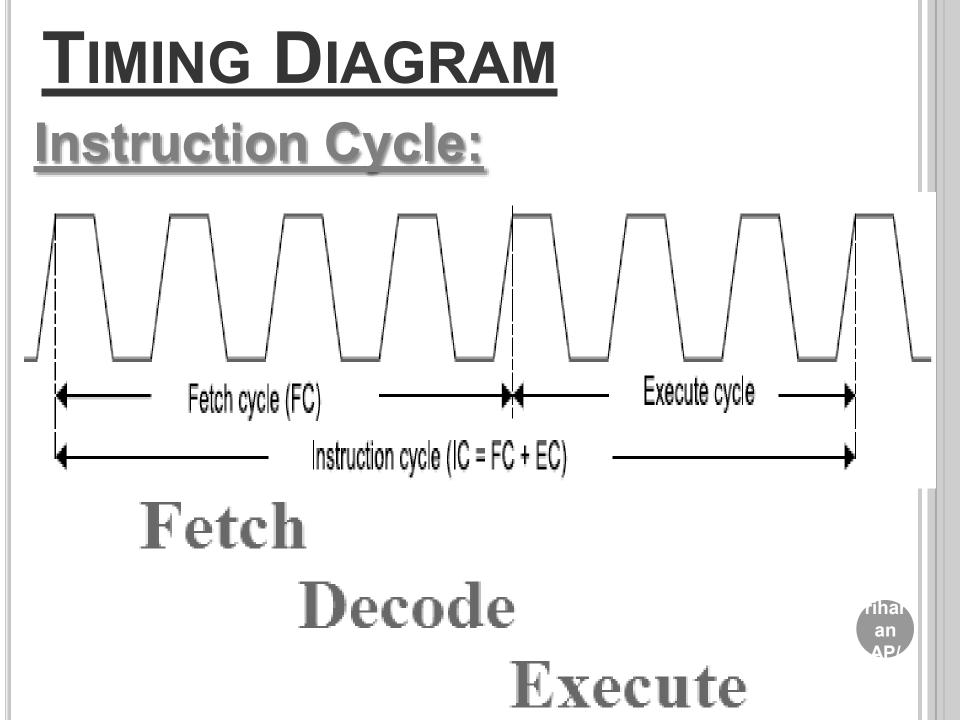

# FETCHING & EXECUTION CYCLES

## Fetching Cycles

- The fetch cycle takes the instruction required from memory, stores it in the instruction register, and

- moves the program counter on one so that it points to the next instruction.

## <u>Execute cycle</u>

- The actual actions which occur during the execute cycle of an instruction.

- depend on both the instruction itself and the addressing mode specified to be used to access the data that may be required.

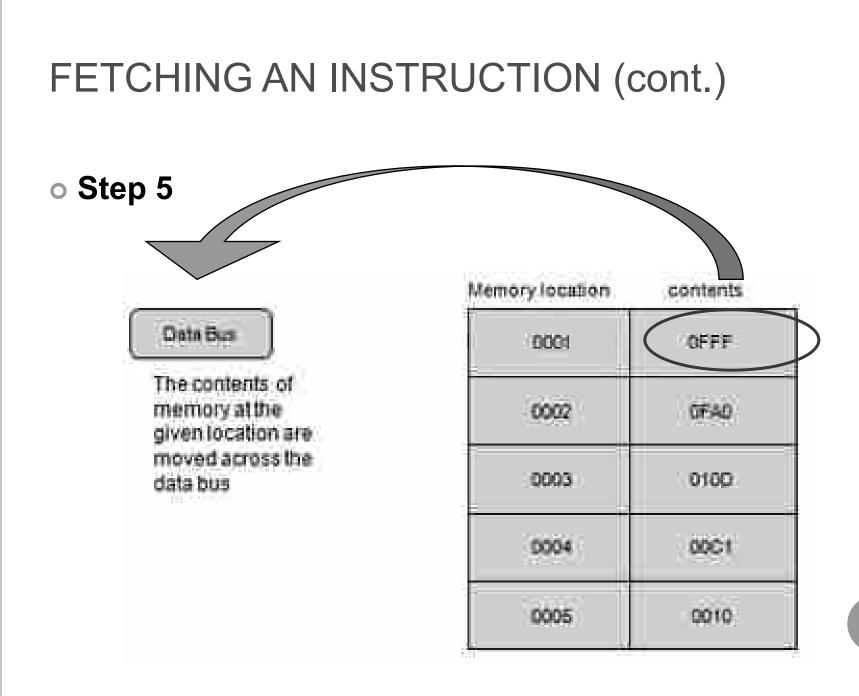

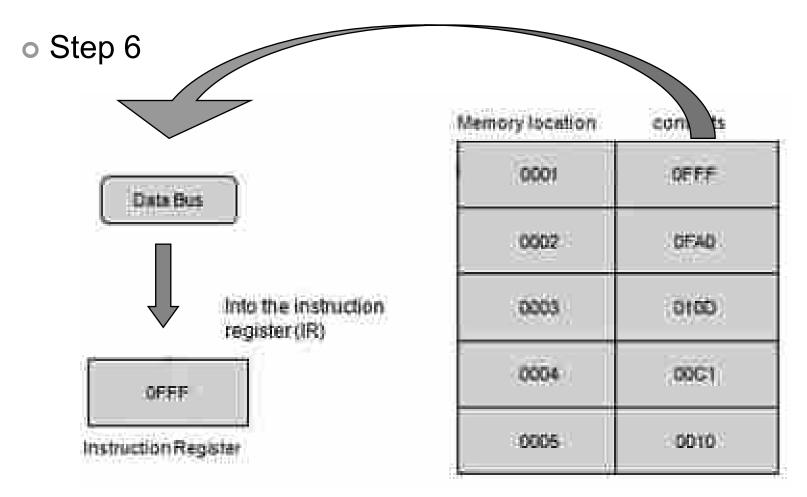

## FETCHING AN INSTRUCTION

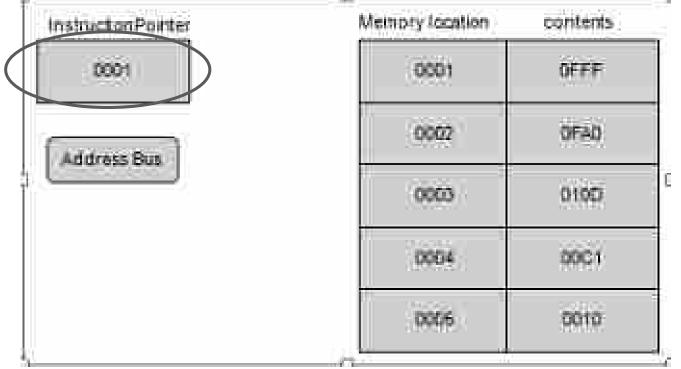

## o Step 1

Instruction pointer (program counter) hold the address of the next instruction to be fetch.

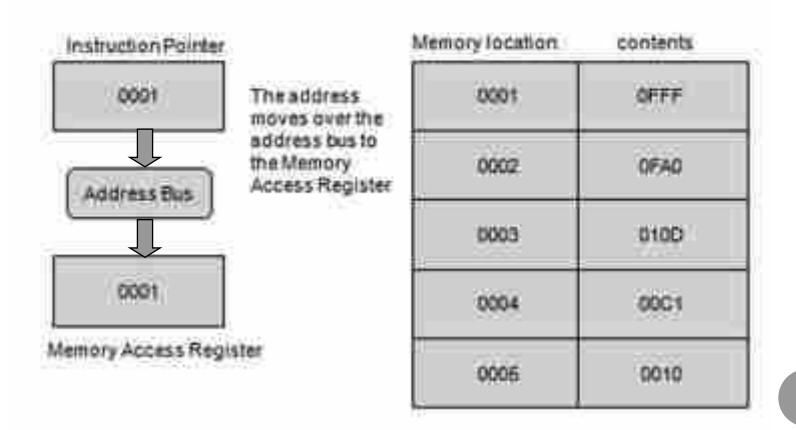

# FETCHING AN INSTRUCTION (cont.)Step 2

Contents of the Program Counter are passed across the Address Bus

| Memory location | contenta |

|-----------------|----------|

| 0001            | OFFF     |

| 0002            | €FA0     |

| 0003            | 0100     |

| 0004            | 0001     |

| 3005            | 0010     |

# FETCHING AN INSTRUCTION (cont.)

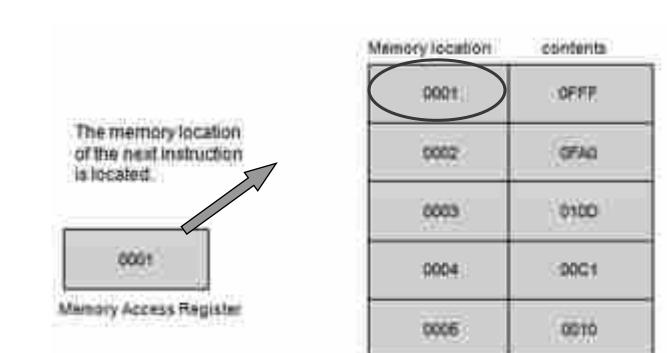

#### o Step 3

# FETCHING AN INSTRUCTION (cont.)

#### o Step 4

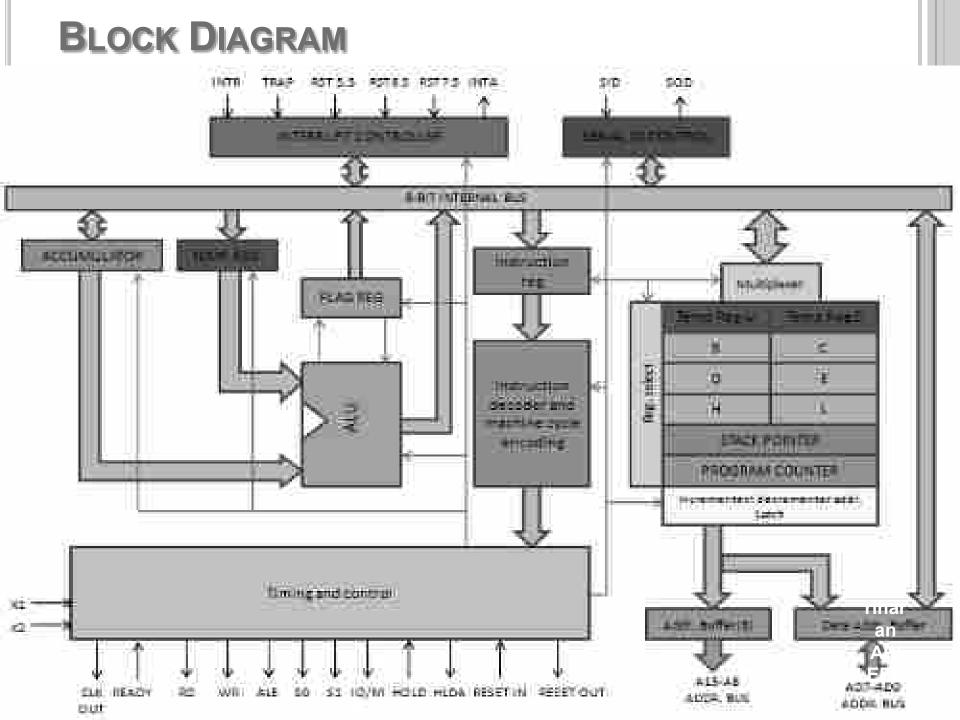

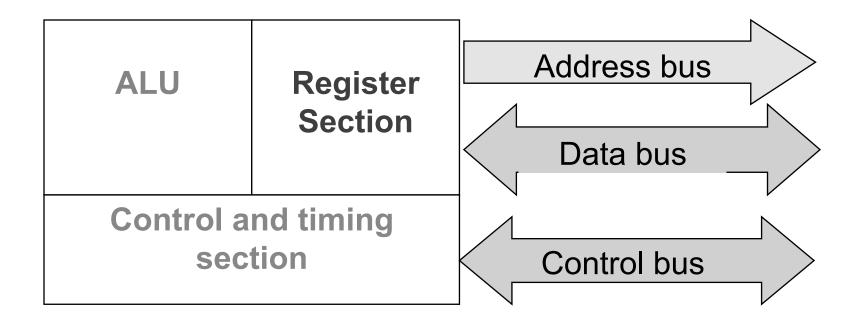

# INTERNAL STRUCTURE AND BASIC OPERATION OF MICROPROCESSOR

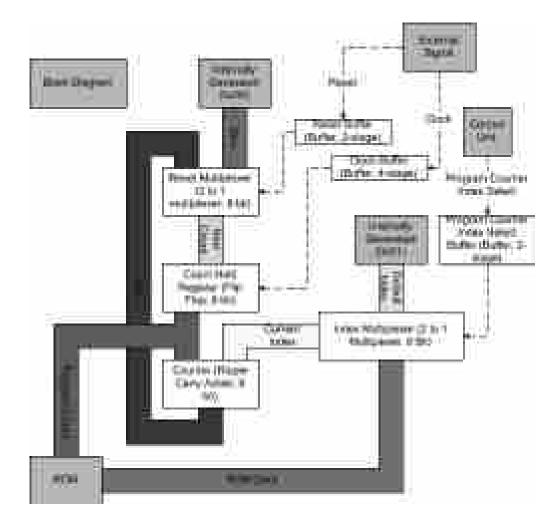

#### Block diagram of a microprocessor

# ARITHMETIC AND LOGIC UNIT (ALU)

- The component that performs the arithmetic and logical operations

- the most important components in a microprocessor, and is typically the part of the processor that is designed first.

- able to perform the basic logical operations (AND, OR), including the addition operation.

- The inclusion of inverters on the inputs enables the same ALU hardware to perform the subtraction operation (adding an inverted operand), and the operations NAND and NOR.

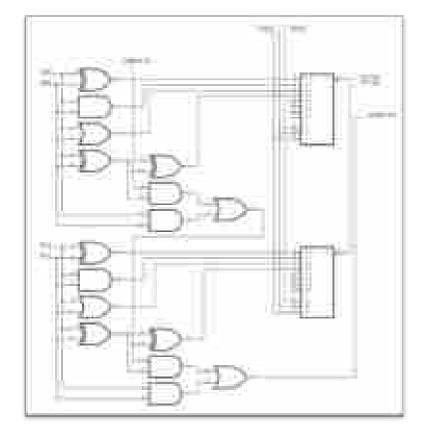

# INTERNAL STRUCTURE OF ALU

2 bits of ALU

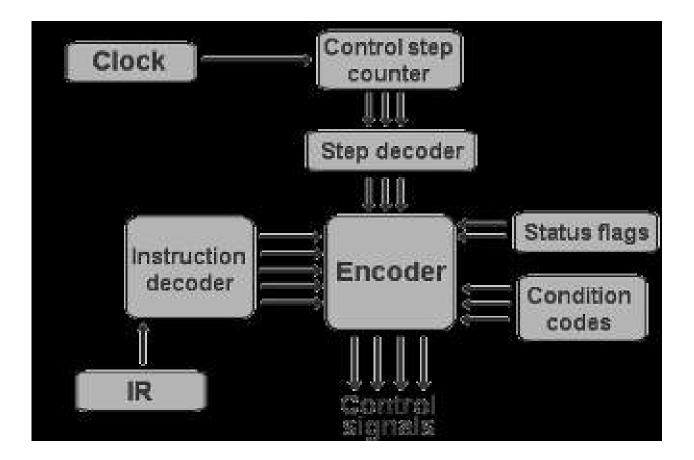

# CONTROL UNIT

- The circuitry that controls the flow of information through the processor, and coordinates the activities of the other units within it.

- In a way, it is the "brain within the brain", as it controls what happens inside the processor, which in turn controls the rest of the PC.

- On a regular processor, the control unit performs the tasks of fetching, decoding, managing execution and then storing results.

## INTERNAL STRUCTURE OF CONTROL UNIT

## **REGISTER SETS**

- The register section/array consists completely of circuitry used to temporarily store data or program codes until they are sent to the ALU or to the control section or to memory.

- The number of registers are different for any particular CPU and the more register a CPU have will result in easier programming tasks.

- Registers are normally measured by the number of <u>bits</u> they can hold, for example, an "<u>8-bit</u> register" or a "<u>32-bit</u> register".

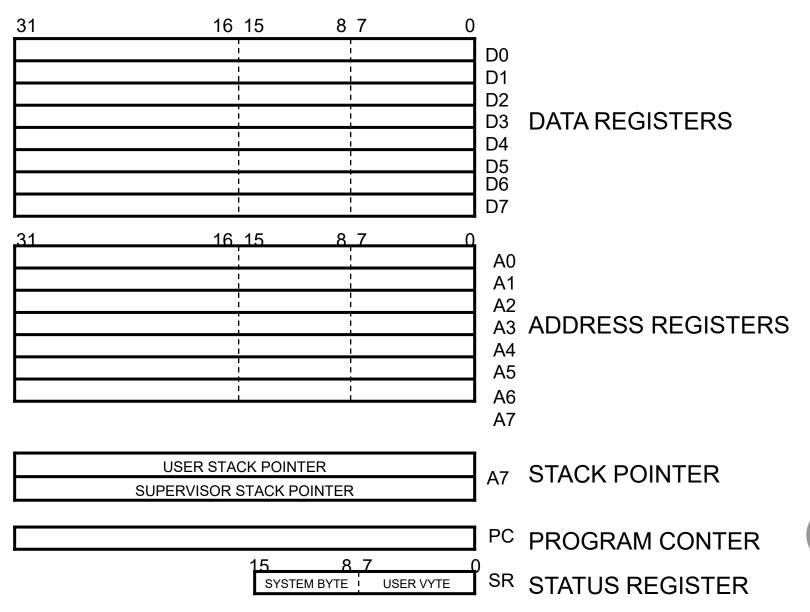

# REGISTER IN MOTOROLA 68000 MICROPROCESSOR

## ACCUMULATOR

- a register in which intermediate arithmetic and logic results are stored.

- example for accumulator use is summing a list of numbers.

- The accumulator is initially set to zero, then each number in turn is added to the value in the accumulator.

- Only when all numbers have been added is the result held in the accumulator written to main memory or to another, non-accumulator, CPU register.

# CONDITION CODE REGISTER (CCR)

• an 8 bit register used to store the status of CPU, such as carry, zero, overflow and half carry.

| Flag | Name                | Description                                                                                                                                                                                                                                                                                                   |

|------|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Z    | Zero flag           | Indicates that the result of a mathematical or logical operation was zero.                                                                                                                                                                                                                                    |

| с    | Carry flag          | Indicates that the result of an operation produced an answer greater<br>than the number of available bits. (This flag may also be set before a<br>mathematical operation as an extra operand to certain instructions, e.g.<br>"add with carry".)                                                              |

| x    | Extend flag         | Masks the XIRQ request when set. It is set by the hardware and cleared by the software as well is set by unmaskable XIRQ.                                                                                                                                                                                     |

| N    | Negative/ Sign flag | Indicates that the result of a mathematical operation is negative. In<br>some processors, the N and S flags have different meanings: the S flag<br>indicates whether a subtraction or addition has taken place, whereas<br>the N flag indicates whether the last operation result is positive or<br>negative. |

| v    | Overflow Flag       | Indicates that the result of an operation has overflowed according to the CPU's word representation, similar to the carry flag but for signed operations.                                                                                                                                                     |

| I    | interrupts          | Interrupts can be enabled or disabled by respectively setting or clearing this flag. Modifying this flag may be restricted to programs executing in supervisor mode                                                                                                                                           |

# PROGRAM COUNTER (PC)

- a 16 bit register, used to store the next address of the operation code to be fetched by the CPU.

- Not much use in programming, but as an indicator to user only.

- Purpose of PC in a Microprocessor

- to store address of tos (top of stack)

- to store address of next instruction to be executed.

- count the number of instructions.

- to store base address of the stack.

## INTERNAL STRUCTURE OF PC

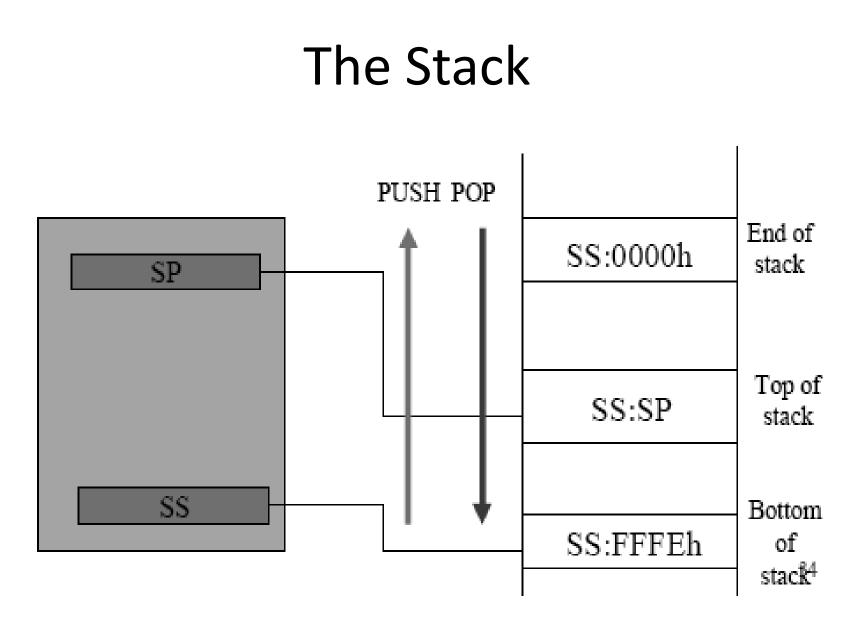

# STACK POINTER (SP)

- The stack is configured as a data structure that grows downward from high memory to low memory.

- At any given time, the SP holds the 16-bit address of the next free location in the stack.

- The stack acts like any other stack when there is a subroutine call or on an interrupt. ie. pushing the return address on a jump, and retrieving it after the operation is complete to come back to its original location.

## BUS SYSTEM

a subsystem that transfers data between computer components inside a computer or between computers.

4 PCI Express bus card slots (from top to bottom: x4, x16, x1 and x16), compared to a traditional 32-bit PCI bus card slot (very bottom).

## BUS SYSTEM CONNECTION

## DATA BUS

# • The data bus is 'bi-directional'

- data or instruction codes from memory or input/output.are transferred into the microprocessor

- the result of an operation or computation is sent out from the microprocessor to the memory or input/output.

- Depending on the particular microprocessor, the data bus can handle 8 bit or 16 bit data.

## ADDRESS BUS

- The address bus is 'unidirectional', over which the microprocessor sends an address code to the memory or input/output.

- The size (width) of the address bus is specified by the number of bits it can handle.

- The more bits there are in the address bus, the more memory locations a microprocessor can access.

- A 16 bit address bus is capable of addressing 65,536 (64K) addresses.

#### CONTROL BUS

• The control bus is used by the microprocessor to send out or receive timing and control signals in order to coordinate and regulate its operation and to communicate with other devices, i.e. memory or input/output.

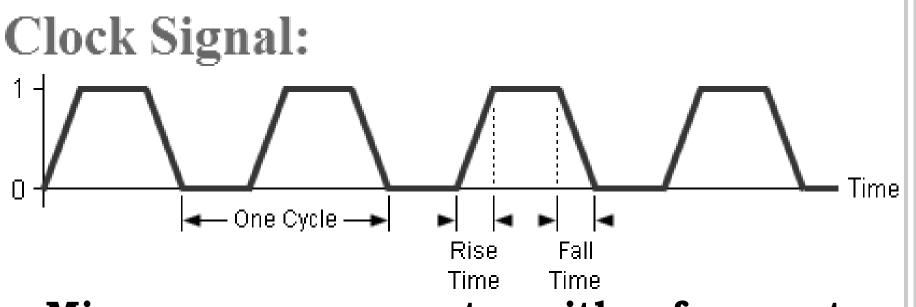

#### MICRO PROCESSOR CLOCK

- Also called clock rate, the speed at which a microprocessor executes instructions. Every computer contains an internal clock that regulates the rate at which instructions are executed and synchronizes all the various computer components.

- The CPU requires a fixed number of clock ticks (or clock cycles) to execute each instruction. The faster the clock, the more instructions the CPU can execute per second. Clock speeds are expressed in megahertz (MHz) or gigahertz ((GHz).

- Some microprocessors are superscalar, which means that they can execute more than one instruction per clock cycle.

- Like CPUs, expansion buses also have clock speeds. Ideally, the CPU clock speed and the bus clock speed should be the same so that neither component slows down the other. In practice, the bus clock speed is often slower than the CPU clock speed, which creates a bottleneck. This is why new local buses, such as AGP, have been developed.

#### EXAMPLES OF MICRO PROCESSOR

Intel 8085Intel 8086

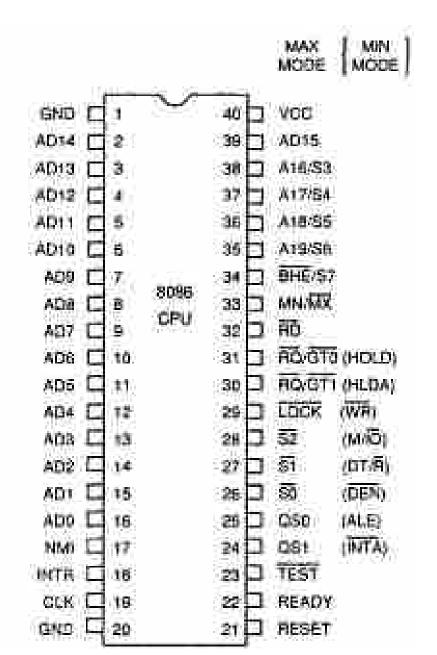

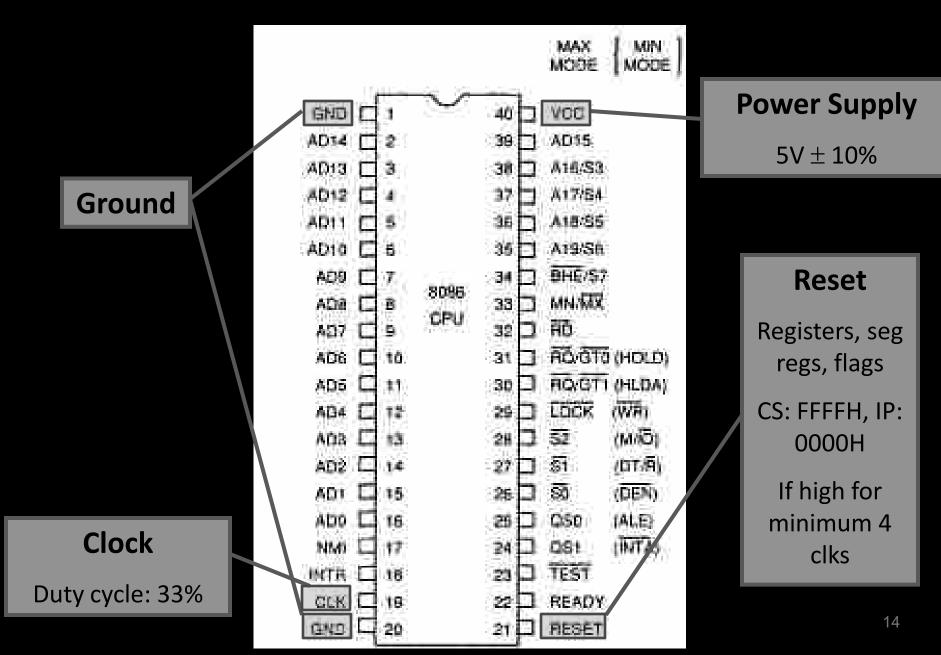

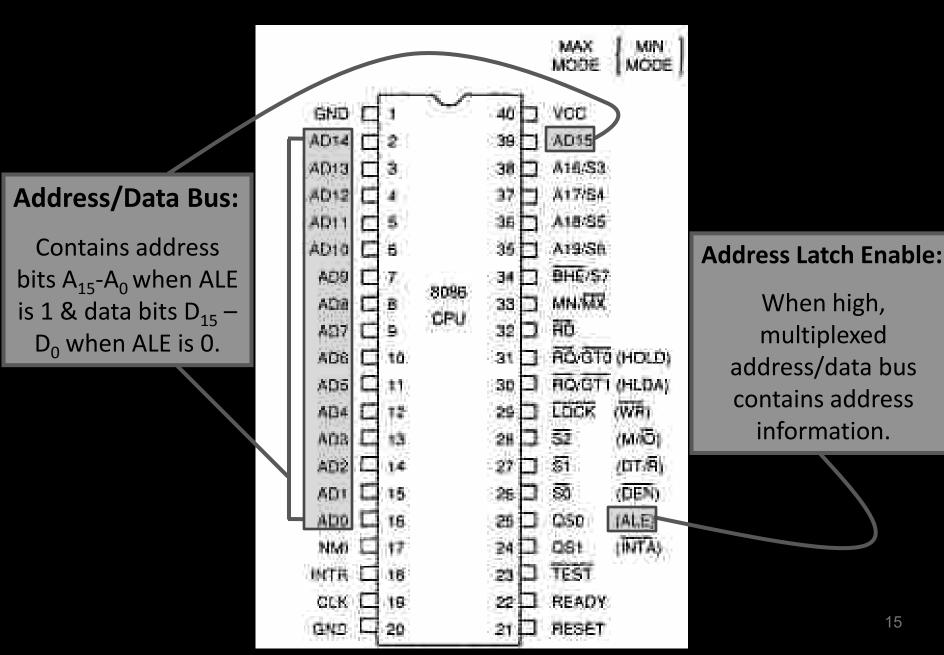

#### 8086

- The 8086 is a 16-bit microprocessor chip designed by Intel, which gave rise to the x86 architecture; development work on the 8086 design started in the spring of 1976 and the chip was introduced to the market in the summer of 1978.

- The Intel 8088, released in 1979, was a slightly modified chip with an external 8-bit data bus (allowing the use of cheaper and fewer supporting logic chips and is notable as the processor used in the original IBM PC.

|            |          |        |      | MAR<br>MORE       | [ um ]      |

|------------|----------|--------|------|-------------------|-------------|

| 080-E      | ;        | 9      | - 44 | D Vec             | Accession 1 |

| 4014 12    |          |        | .99  | TADI .            |             |

| AP13 E     | 3        |        | - 26 | 1416/35           |             |

| AG14 E     | 4        |        | -37  | 1419/2=           |             |

| (#1) (E    | ÷ .      |        | : 54 | JATA/SIL          |             |

| AB10 C     |          |        | 36   | <b>1</b> 449/50   |             |

| 40910      | 2        |        | -\$4 | CLIGHT, W         |             |

| A10 C      | ê.,      |        | -33  | CININ/55          |             |

| 200        | ÷        | ains i | 36   | 160               |             |

| AD: L      | ¢0       | 694    | -37  | ⊐ 89/4 <b>1</b> 8 | 0.0400      |

| 101.22     | 10 C     |        | -36  | 185/671           | peutos,     |

| 30412      | 12       |        | 125  | LOCK              | (88)        |

| 444 C      | (3) ·    |        | 23   | 744               | 04/192      |

| ANDER      | 14       |        | 32   | 11                | 1093/99     |

| 4640       | £3.      |        | -30  | 13 KW             | (000)       |

| ADO C      | 10       |        | 24   | <b>1946</b>       | CASES       |

| <b>NME</b> | 12       |        | -24  | 2031              | 00000       |

| HITE LE    | ιA.      |        | 20   | <b>1</b> 1157     | 101022-001  |

| GRE        | <b>1</b> |        | - 22 | <b>TREAD</b>      |             |

| 0.02       | 10       |        | *    | 21/45327          |             |

#### 8085

- The Intel 8085 is an 8-bit microprocessor introduced by Intel in 1977.

- It was binary-compatible with the more-famous Intel 8080 but required less supporting hardware, thus allowing simpler and less expensive microcomputer systems to be built.

| An Intel 8085AH processor.        |                           |  |

|-----------------------------------|---------------------------|--|

| Produced                          | From 1977 to<br>1990s     |  |

| Common manufacturer(s)            | •Intel and several others |  |

| Max. <u>CPU</u> <u>clock rate</u> | 3,5 and<br>6 MHz          |  |

| Instruction set                   | pre <u>x86</u>            |  |

| Package(s)                        | •40 pin <u>DIP</u>        |  |

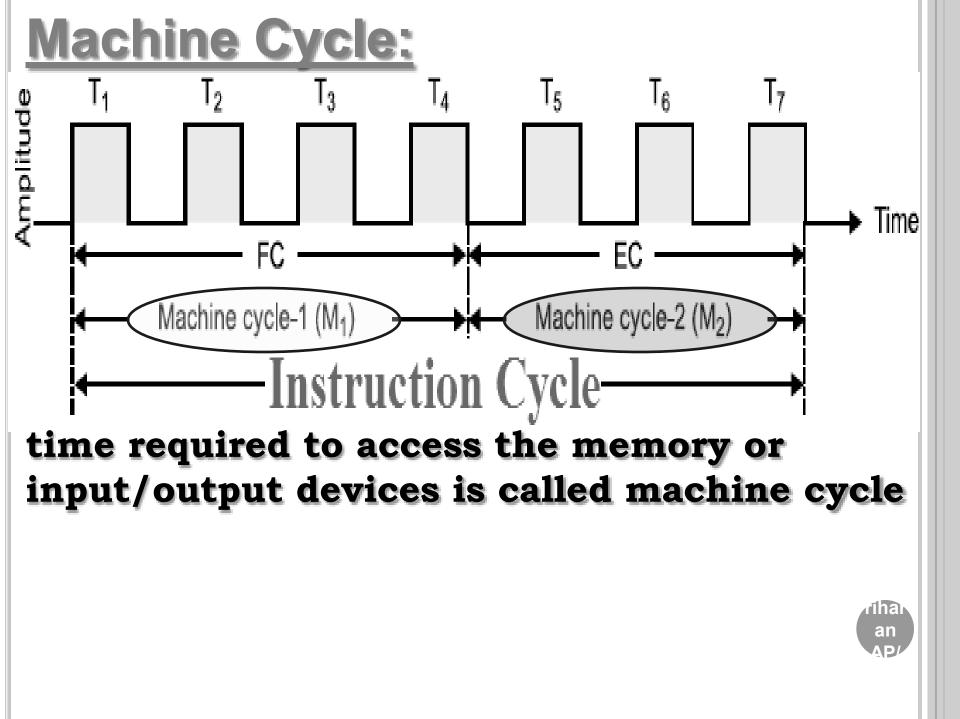

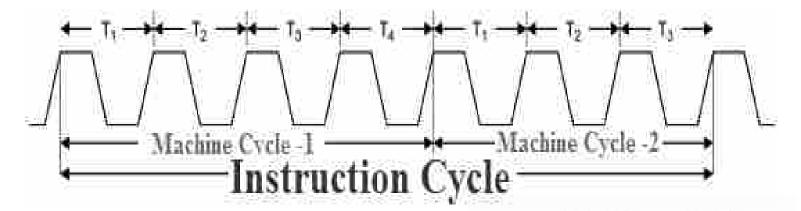

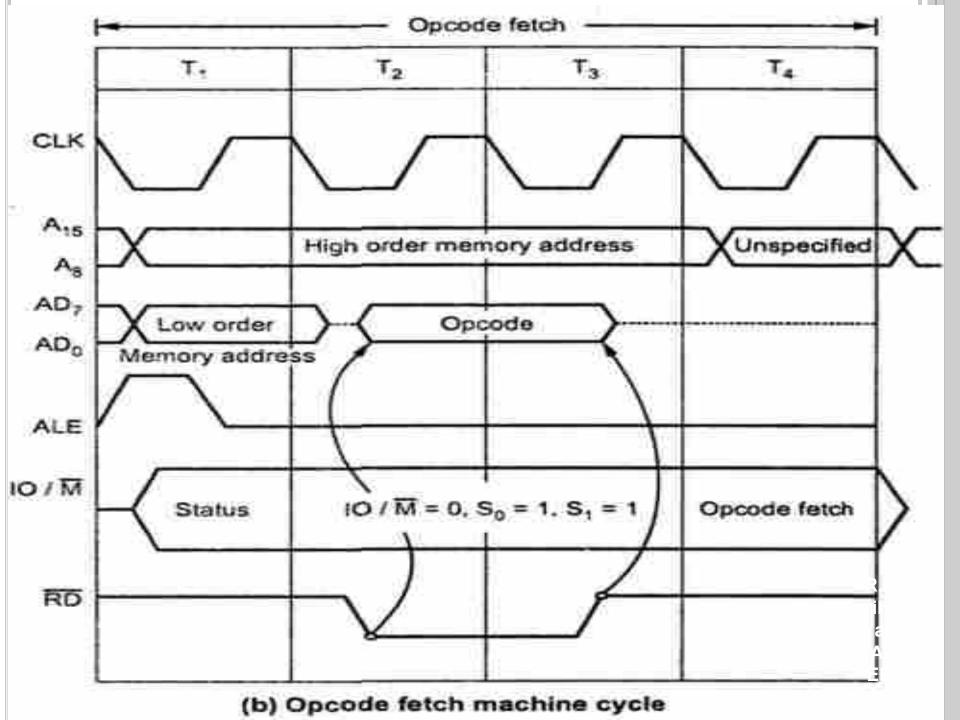

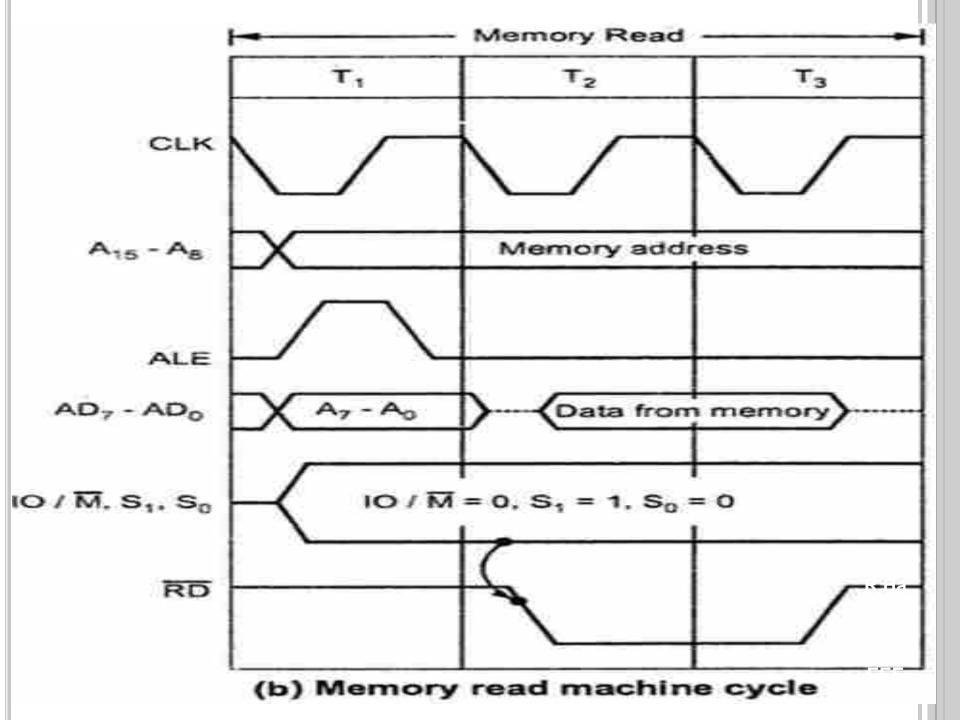

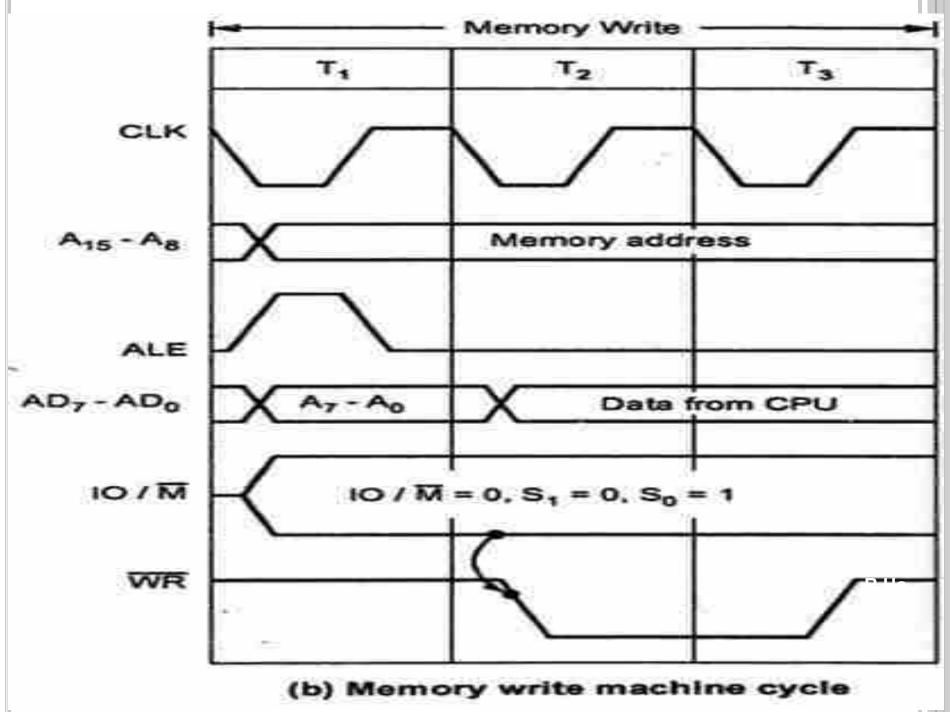

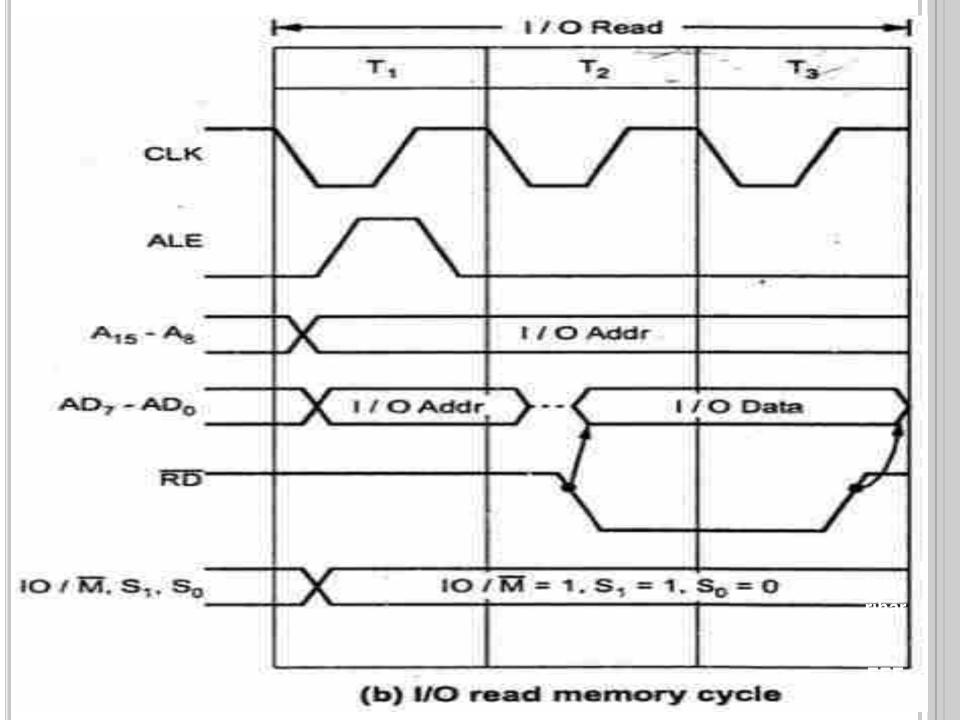

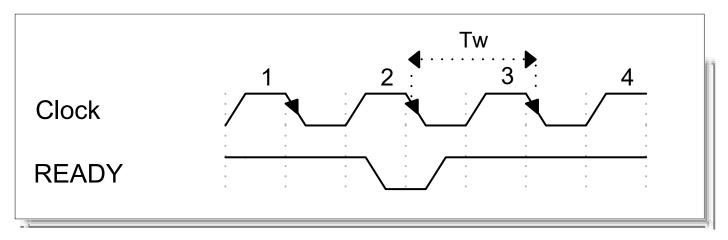

#### The machine cycle and instruction cycle takes <u>multiple</u> <u>clock periods</u>.

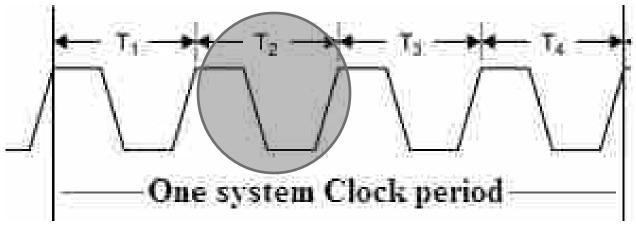

# A portion of an operation carried out in one system clock period is called as T-state

an an

- Microprocessor operates with <u>reference</u> to clock signals.

- X1 and X2 we provide clock signals and this frequency is divided by two.

- This frequency is called as the operating frequency.

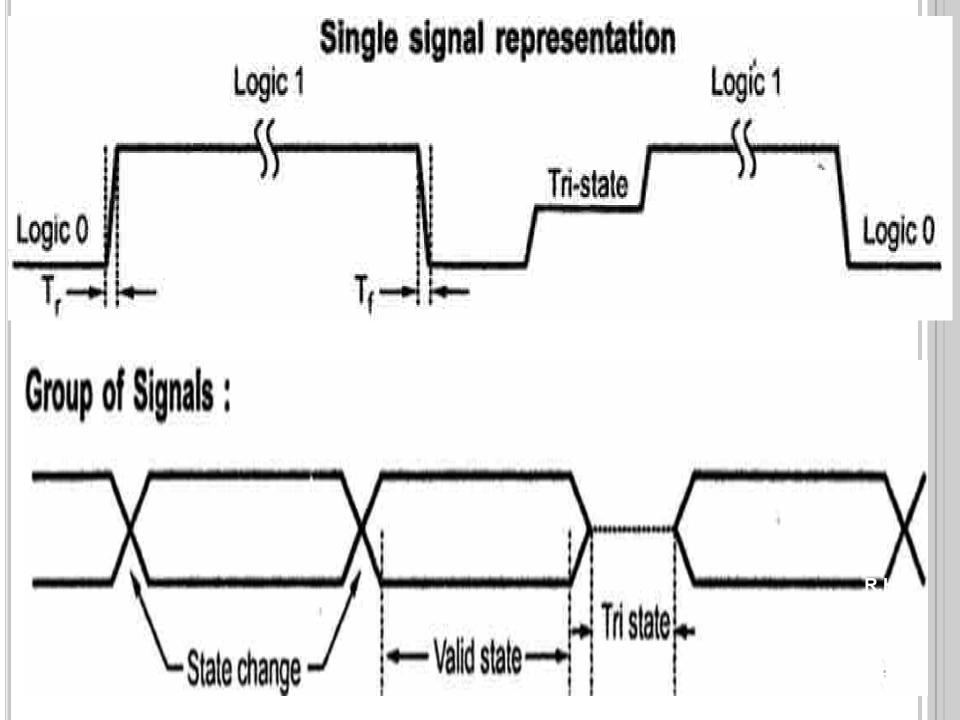

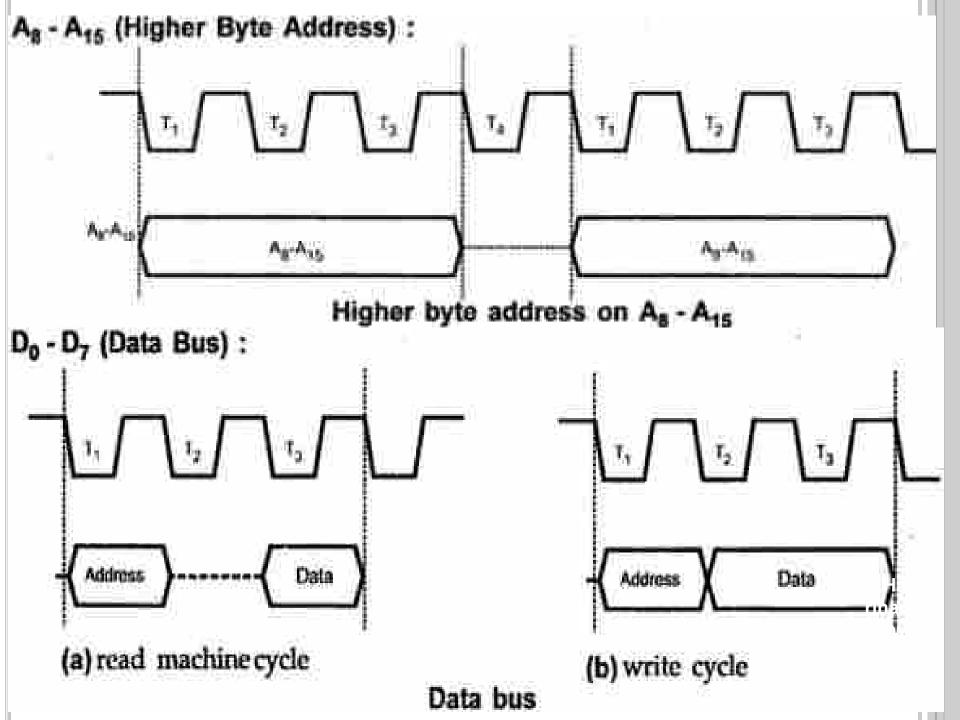

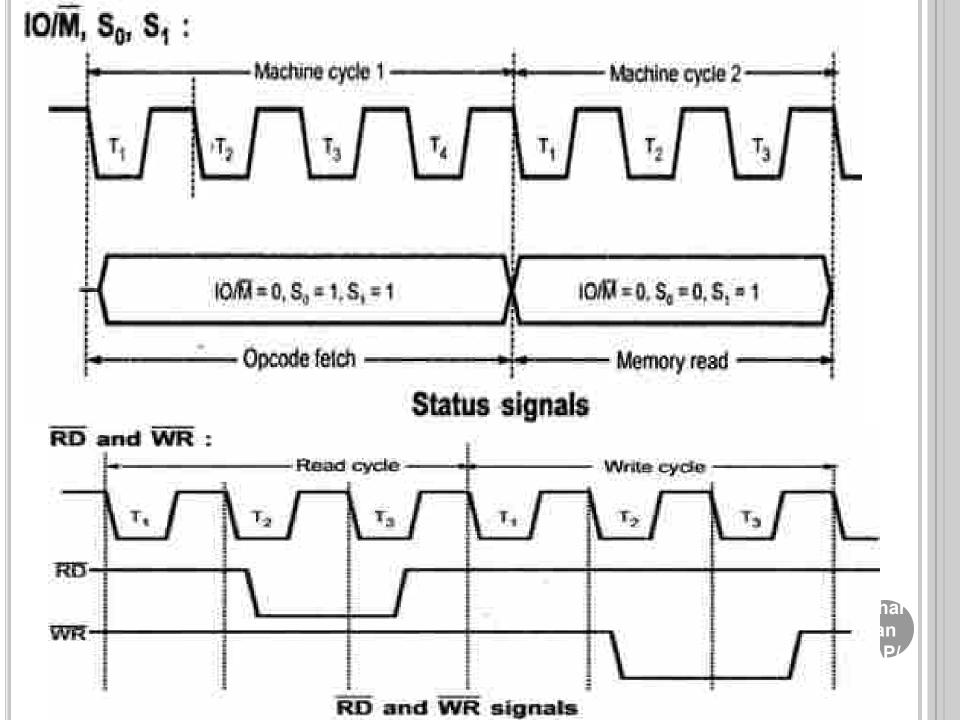

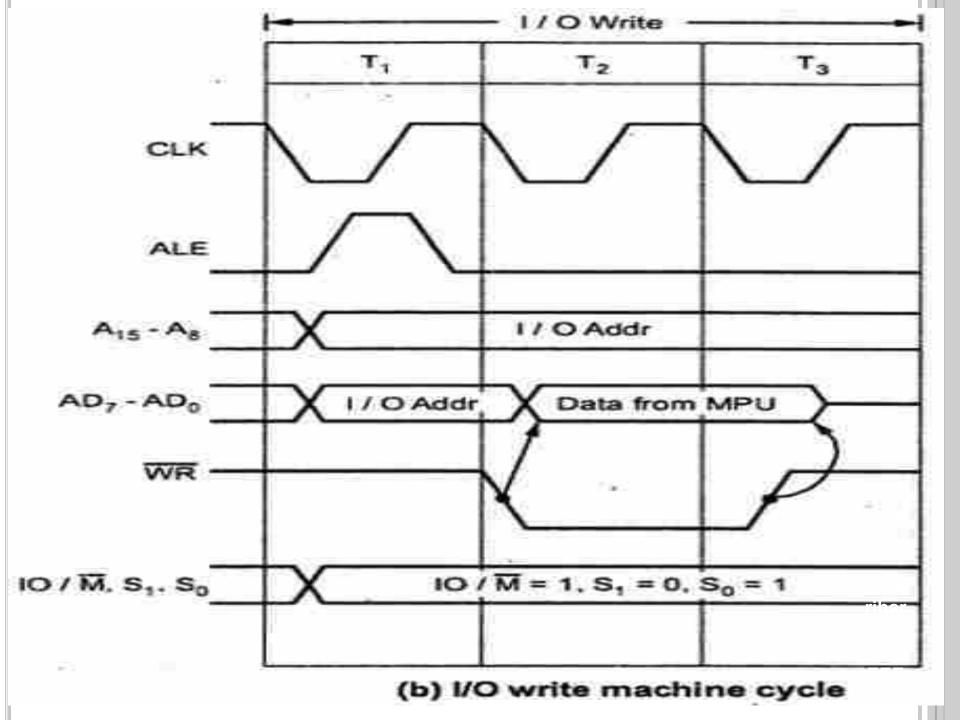

Rule for timing diagram:

- 1. ALE=1. T1 States.

- 2. AO-A7=Group Signal. T1 States.

- 3. A8-A15 = Group Signal. T1,T2,T3 States.

- 4. D0-D7=Group Signal. Read Cycle : T1-Address, T3 - Data Write Cycle : T1-Address, T2,T3 -Data

- 5. IO/M S0,S1 = Group Signal. T1,T2,T3,T4 States.

- 6. RD,WR = 0. T2,T3 States

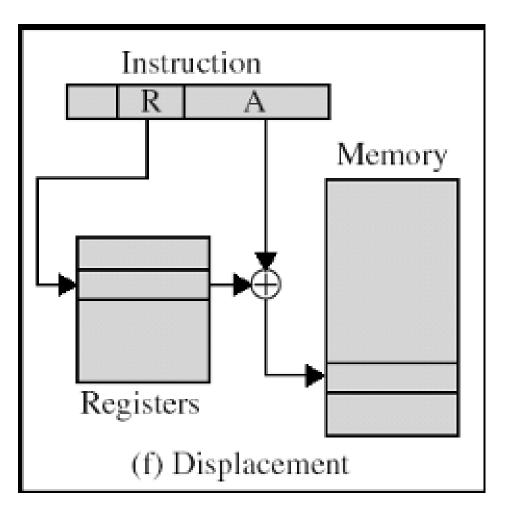

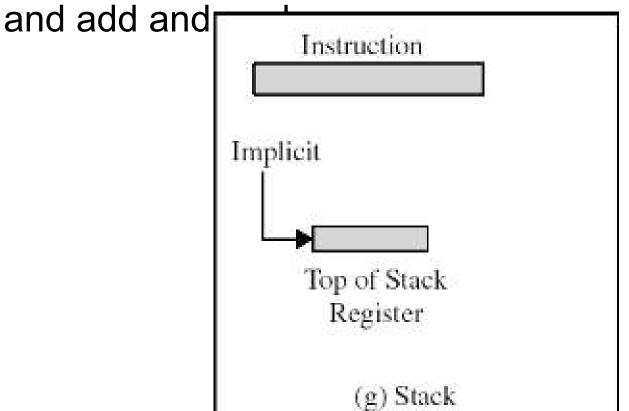

# **Addressing Modes**

#### **TYPES OF ADDRESSING MODES**

• Intel 8085 uses the following addressing modes:

rīhai an

- 1. Direct Addressing Mode

- 2. Register Addressing Mode

- 3. Register Indirect Addressing Mode

- 4. Immediate Addressing Mode

- 5. Implicit Addressing Mode

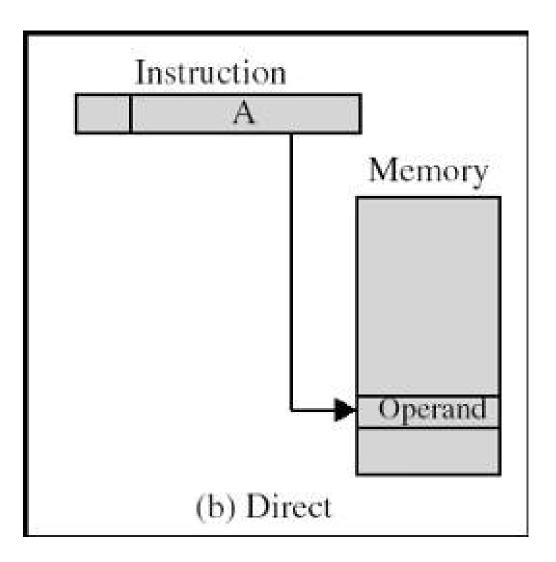

#### DIRECT ADDRESSING MODE

In this mode, the address of the operand is given in the instruction itself.

####

- 2500 H is the address of source.

- Accumulator is the destination.

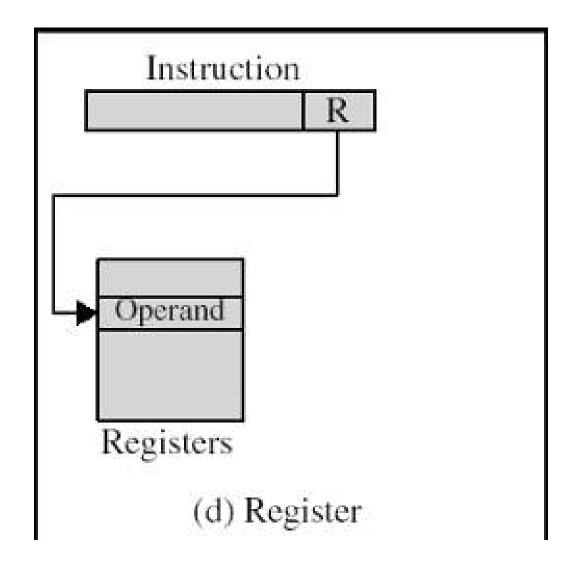

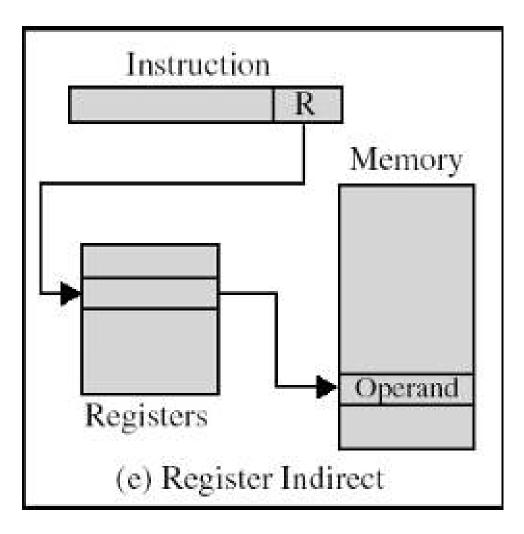

#### **REGISTER ADDRESSING MODE**

In this mode, the operand is in general purpose register.

- MOV is the operation.

- B is the source of data.

- A is the destination.

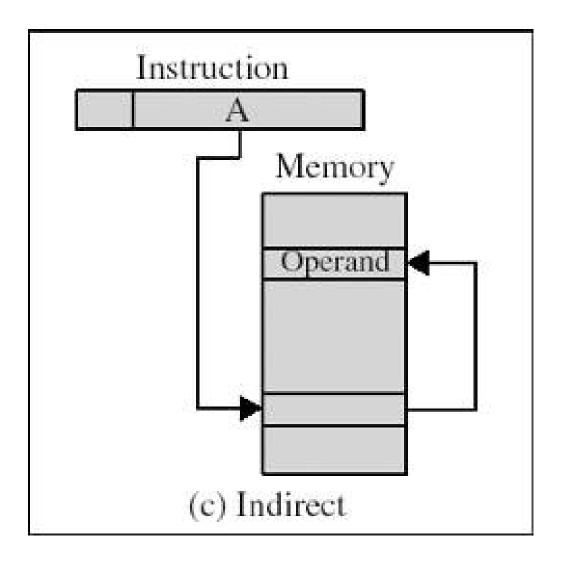

### **REGISTER INDIRECT ADDRESSING MODE**

• In this mode, the address of operand is specified by a register pair.

MOV A, M Move data from memory location specified by H-L pair to accumulator.

- MOV is the operation.

- M is the memory location specified by H-L register pair.

- A is the destination.

#### IMMEDIATE ADDRESSING MODE

• In this mode, the operand is specified within the instruction itself.

#### MVI A, 05 H Move 05 H in accumulator.

- MVI is the operation.

- o 05 H is the immediate data (source).

- A is the destination.

#### IMPLICIT ADDRESSING MODE

If address of source of data as well as address of destination of result is fixed, then there is no need to give any operand along with the instruction.

#### CMA

#### Complement accumulator.

- CMA is the operation.

- A is the source.

- A is the destination.

### **8085 Instruction Set**

## Instruction Set of 8085

- An instruction is a binary pattern designed inside a microprocessor to perform a specific function.

- The entire group of instructions that a microprocessor supports is called *Instruction Set*.

- 8085 has 246 instructions.

- Each instruction is represented by an 8-bit binary value.

- These 8-bits of binary value is called Op-Code or Instruction Byte.

## **Classification of Instruction Set**

- Data Transfer Instruction

- Arithmetic Instructions

- Logical Instructions

- Branching Instructions

- Control Instructions

- These instructions move data between registers, or between memory and registers.

- These instructions copy data from source to destination.

While copying, the contents of source are not modified.

| Opcode     | Operand | Description                      |

|------------|---------|----------------------------------|

| MOV        | Rd, Rs  | Copy from source to destination. |

| 0500000000 | M, Rs   |                                  |

|            | Rd, M   |                                  |

- This instruction copies the contents of the source register into the destination register.

- The contents of the source register are not altered.

- If one of the operands is a memory location, its location is specified by the contents of the HL registers.

- \* Example: MOV B, C or MOV B, M

| Opcode | Operand             | Description          |  |

|--------|---------------------|----------------------|--|

| MVI    | Rd, Data<br>M, Data | Move immediate 8-bit |  |

- The 8-bit data is stored in the destination register or memory.

- If the operand is a memory location, its location is specified by the contents of the H-L registers.

- Example: MVI B, 57H or MVI M, 57H

| Opcode | Operand        | Description      |

|--------|----------------|------------------|

| LDA    | 16-bit address | Load Accumulator |

- The contents of a memory location, specified by a 16bit address in the operand, are copied to the accumulator.

- The contents of the source are not altered.

- Example: LDA 2034H

| Opcode | Operand              | Description               |

|--------|----------------------|---------------------------|

| LDAX   | B/D Register<br>Pair | Load accumulator indirect |

- The contents of the designated register pair point to a memory location.

- This instruction copies the contents of that memory location into the accumulator.

- The contents of either the register pair or the memory location are not altered.

- Example: LDAX B

| Opcode | Operand                   | Description                  |

|--------|---------------------------|------------------------------|

| LXI    | Reg. pair, 16-bit<br>data | Load register pair immediate |

- This instruction loads 16-bit data in the register pair.

- Example: LXI H, 2034 H

| Opcode | Operand        | Description               |

|--------|----------------|---------------------------|

| LHLD   | 16-bit address | Load H-L registers direct |

- This instruction copies the contents of memory location pointed out by 16-bit address into register L.

- It copies the contents of next memory location into register H.

- Example: LHLD 2040 H

| Opcode | Operand        | Description              |

|--------|----------------|--------------------------|

| STA    | 16 bit address | Store accumulator direct |

The contents of accumulator are copied into the memory location specified by the operand.

• Example: STA 2500 H

| Opcode | Operand   | Description                |  |

|--------|-----------|----------------------------|--|

| STAX   | Reg. pair | Store accumulator indirect |  |

The contents of accumulator are copied into the memory location specified by the contents of the register pair.

#### • Example: STAX B

| Opcode | Operand        | Description                 |  |

|--------|----------------|-----------------------------|--|

| SHLD   | 16-bit address | Store II-L registers direct |  |

- The contents of register L are stored into memory location specified by the 16-bit address.

- The contents of register H are stored into the next memory location.

- Example: SHLD 2550 H

| Opcode | Operand | Description            |

|--------|---------|------------------------|

| XCHG   | None    | Exchange II-L with D-E |

- The contents of register H are exchanged with the contents of register D.

- The contents of register L are exchanged with the contents of register E.

- Example: XCHG

| Opcode | Operand | Description                             |

|--------|---------|-----------------------------------------|

| SPHL   | None    | Copy H-L pair to the Stack Pointer (SP) |

• This instruction loads the contents of H-L pair into SP.

#### • Example: SPHL

| Opcode | Operand | Description                    |  |

|--------|---------|--------------------------------|--|

| XTHL   | None    | Exchange H-L with top of stack |  |

- The contents of L register are exchanged with the location pointed out by the contents of the SP.

- The contents of H register are exchanged with the next location (SP + 1).

#### • Example: XTHL

| Opcode | Operand | Description                            |

|--------|---------|----------------------------------------|

| PCHL   | None    | Load program counter with H-L contents |

- The contents of registers H and L are copied into the program counter (PC).

- The contents of H are placed as the high-order byte and the contents of L as the low-order byte.

- Example: PCHL

| Opcode | Operand   | Description                   |

|--------|-----------|-------------------------------|

| PUSH   | Reg. pair | Push register pair onto stack |

- The contents of register pair are copied onto stack.

- SP is decremented and the contents of high-order registers (B, D, H, A) are copied into stack.

- SP is again decremented and the contents of low-order registers (C, E, L, Flags) are copied into stack.

- Example: PUSH B

| Oprode | Operand  | Description                |

|--------|----------|----------------------------|

| POP    | Reg. рай | Pop stack to register pair |

- The contents of top of stack are copied into register pair.

- The contents of location pointed out by SP are copied to the low-order register (C, E, L, Flags).

- SP is incremented and the contents of location are copied to the high-order register (B, D, H, A).

- Example: POP H

| Opcode | Operand               | Description                                                 |

|--------|-----------------------|-------------------------------------------------------------|

| OUT    | 8-bit port<br>address | Copy data from accumulator to a port with 8-<br>bit address |

- The contents of accumulator are copied into the I/O port.

- Example: OUT 78 H

| Opcode | Operand               | Description                                                 |

|--------|-----------------------|-------------------------------------------------------------|

| IN     | 8-bit port<br>address | Copy data to accumulator from a port with 8-<br>bit address |

The contents of I/O port are copied into accumulator.

#### • Example: IN 8C H

# Addition

- Any 8-bit number, or the contents of register, or the contents of memory location can be added to the contents of accumulator.

- The result (sum) is stored in the accumulator.

- No two other 8-bit registers can be added directly.

- Example: The contents of register B cannot be added directly to the contents of register C.

## Subtraction

- Any 8-bit number, or the contents of register, or the contents of memory location can be subtracted from the contents of accumulator.

- The result is stored in the accumulator.

- Subtraction is performed in 2's complement form.

- If the result is negative, it is stored in 2's complement form.

- No two other 8-bit registers can be subtracted directly.

# Increment / Decrement

- The 8-bit contents of a register or a memory location can be incremented or decremented by 1.

- The 16-bit contents of a register pair can be incremented or decremented by 1.

- Increment or decrement can be performed on any register or a memory location.

| Opcode | Operand | Description                           |

|--------|---------|---------------------------------------|

| ADD    | R<br>M  | Add register or memory to accumulator |

- The contents of register or memory are added to the contents of accumulator.

- The result is stored in accumulator.

- If the operand is memory location, its address is specified by H-L pair.

- All flags are modified to reflect the result of the addition.

- Example: ADD B or ADD M

| Opcode | Operand | Description                                         |

|--------|---------|-----------------------------------------------------|

| ADC    | R<br>M  | Add register or memory to accumulator with<br>earsy |

- The contents of register or memory and Carry Flag (CY) are added to the contents of accumulator.

- The result is stored in accumulator.

- If the operand is memory location, its address is specified by H-L pair.

- All flags are modified to reflect the result of the addition.

- Example: ADC B or ADC M

| Opcode | Operand    | Description                  |  |

|--------|------------|------------------------------|--|

| ADI    | 8-bit data | Add immediate to accumulator |  |

- The 8-bit data is added to the contents of accumulator.

- The result is stored in accumulator.

- All flags are modified to reflect the result of the addition.

- Example: ADI 45 H

| Opcode | Operand    | Description                             |

|--------|------------|-----------------------------------------|

| ACI    | 8-bit data | Add immediate to accumulator with carry |

- The 8-bit data and the Carry Flag (CY) are added to the contents of accumulator.

- The result is stored in accumulator.

- All flags are modified to reflect the result of the addition.

- Example: ACI 45 H

| Opcode | Operand   | Description                   |  |

|--------|-----------|-------------------------------|--|

| DAD    | Reg. pair | Add register pair to H-L pair |  |

- The 16-bit contents of the register pair are added to the contents of H-L pair.

- The result is stored in H-L pair.

- If the result is larger than 16 bits, then CY is set.

- No other flags are changed.

- Example: DAD B

| Opende | Operand | Description                                  |

|--------|---------|----------------------------------------------|

| SUB    | R<br>M  | Subtract register or memory from accumulator |

- The contents of the register or memory location are subtracted from the contents of the accumulator.

- The result is stored in accumulator.

- If the operand is memory location, its address is specified by H-L pair.

- All flags are modified to reflect the result of subtraction.

- Example: SUB B or SUB M

| Opcode | Operand | Description                                              |

|--------|---------|----------------------------------------------------------|

| SBB    | R<br>M  | Subtract register or memory from accumulator with borrow |

- The contents of the register or memory location and Borrow Flag (i.e. CY) are subtracted from the contents of the accumulator.

- The result is stored in accumulator.

- If the operand is memory location, its address is specified by H-L pair.

- All flags are modified to reflect the result of subtraction.

- Example: SBB B or SBB M

| Opcode | Operand    | Description                         |

|--------|------------|-------------------------------------|

| SUI    | 8-bit data | Subtract immediate from accumulator |

- The 8-bit data is subtracted from the contents of the accumulator.

- The result is stored in accumulator.

- All flags are modified to reflect the result of subtraction.

- Example: SUI 45 H

| Opcode | Operand    | Description                                     |

|--------|------------|-------------------------------------------------|

| SBI    | 8-bit data | Subtract immediate from accumulator with borrow |

- The 8-bit data and the Borrow Flag (i.e. CY) is subtracted from the contents of the accumulator.

- The result is stored in accumulator.

- All flags are modified to reflect the result of subtraction.

- Example: SBI 45 H

| A      | rithme  | tic Instructions                  |

|--------|---------|-----------------------------------|

| Opcode | Operand | Description                       |

| INR    | R<br>M  | Increment register or memory by 1 |

- The contents of register or memory location are incremented by i.

- The result is stored in the same place.

- If the operand is a memory location, its address is specified by the contents of H-L pair.

- Example: INR B or INR M

| Operand | Description                  |

|---------|------------------------------|

| R       | Increment register pair by 1 |

|         | Operand<br>R                 |

- The contents of register pair are incremented by 1.

- The result is stored in the same place.

- Example: INX H

| Opcode | Operand | Description                       |

|--------|---------|-----------------------------------|

| DCR    | R<br>M  | Decrement register or memory by 1 |

- The contents of register or memory location are decremented by 1.

- The result is stored in the same place.

- If the operand is a memory location, its address is specified by the contents of H-L pair.

- Example: DCR B or DCR M

| Opcode | Operand | Description                  |

|--------|---------|------------------------------|

| DCX    | R       | Decrement register pair by 1 |

- The contents of register pair are decremented by 1.

- The result is stored in the same place.

- Example: DCX H

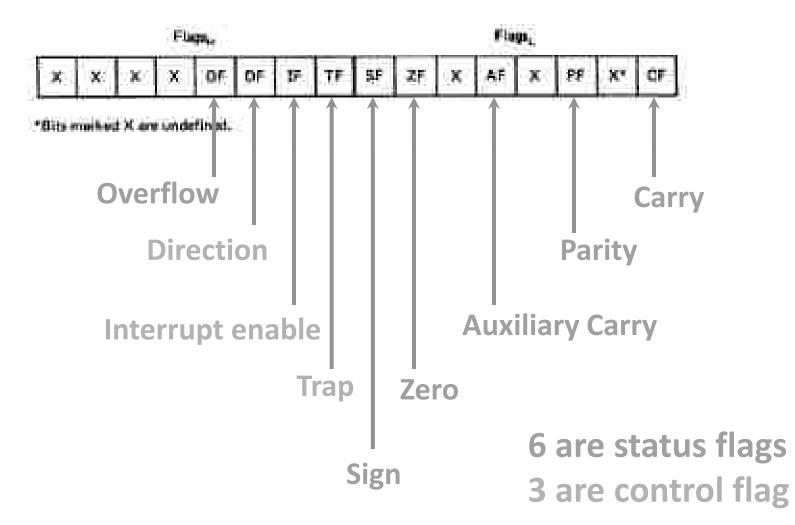

## Logical Instructions

These instructions perform logical operations on data stored in registers, memory and status flags.

- PSW (Program Status word)

- Flag unaffected

- \* affected

- 0 reset

- 1 set

- S Sign (Bit 7)

- Z Zero (Bit 6)

- AC Auxiliary Carry (Bit 4)

- P Parity (Bit 2)

- CY Carry (Bit 0)

# AND, OR, XOR

- Any 8-bit data, or the contents of register, or memory location can logically have

- AND operation

- OR operation

- XOR operation

- with the contents of accumulator.

- The result is stored in accumulator.

# Rotate

Each bit in the accumulator can be shifted either left or right to the next position.

## Compare

- Any 8-bit data, or the contents of register, or memory location can be compares for:

- Equality

- Greater Than

- Less Than

- with the contents of accumulator.

- The result is reflected in status flags.

# **Logical Instructions**

| Opcode | Operand | Description                     |  |

|--------|---------|---------------------------------|--|

| CMP    | R       | Compare register or memory with |  |

|        | М       | accumulator                     |  |

- The contents of the operand (register or memory) are compared with the contents of the accumulator.

- Both contents are preserved .

- The result of the comparison is shown by setting the flags of the PSW as follows:

# **Logical Instructions**

| Opcode | Operand | Description                     |

|--------|---------|---------------------------------|

| CMP    | R       | Compare register or memory with |

|        | М       | accumulator                     |

- if (A) < (reg/mem): carry flag is set</li>

- if (A) = (reg/mem): zero flag is set

- if (A) > (reg/mem): carry and zero flags are reset.

- Example: CMP B or CMP M

|        | Logical    | Instructions                       |

|--------|------------|------------------------------------|

| Opcode | Operand    | Description                        |

| CPI    | 8-bit data | Compare immediate with accumulator |

- The 8-bit data is compared with the contents of accumulator.

- The values being compared remain unchanged.

- The result of the comparison is shown by setting the flags of the PSW as follows:

| Opcode | Operand    | Description                        |

|--------|------------|------------------------------------|

| CPI    | 8-bit data | Compare immediate with accumulator |

- if (A) < data: carry flag is set</li>

- if (A) = data: zero flag is set

- if (A) > data: carry and zero flags are reset

- Example: CPI 89H

| Opposie | Operand | Description                                        |

|---------|---------|----------------------------------------------------|

| ANA     | 8<br>M  | Logical AND register or memory with<br>accumulator |

- The contents of the accumulator are logically ANDed with the contents of register or memory.

- The result is placed in the accumulator.

- If the operand is a memory location, its address is specified by the contents of H-L pair.

- S, Z, P are modified to reflect the result of the operation.

- CY is reset and AC is set.

- Example: ANA B or ANA M.

|         | Description                       | Operand    | Opcode |

|---------|-----------------------------------|------------|--------|

| mulator | Logical AND immediate with accumu | 8-bit data | ANI    |

|         | Logical AND immediate with accu   | 8-bit data | ANI    |

- The contents of the accumulator are logically ANDed with the 8-bit data.

- The result is placed in the accumulator.

- S, Z, P are modified to reflect the result.

- CY is reset, AC is set.

- Example: ANI 86H.

| Opcode | Operand | Description                                       |

|--------|---------|---------------------------------------------------|

| ORA    | R<br>M  | Logical OR register or memory with<br>accumulator |

- The contents of the accumulator are logically ORed with the contents of the register or memory.

- The result is placed in the accumulator.

- If the operand is a memory location, its address is specified by the contents of H-L pair.

- 5. Z. P are modified to reflect the result.

- CY and AC are reset.

- · Example: ORA II of ORA M.

| Opcode | Operand    | Description                           |

|--------|------------|---------------------------------------|

| ORI    | 8-bit data | Logical OR immediate with accumulator |

- The contents of the accumulator are logically ORed with the 8-bit data.

- The result is placed in the accumulator.

- S, Z, P are modified to reflect the result.

- CY and AC are reset.

- Example: ORI 86H.

| Optoile | Operand | Description                                        |

|---------|---------|----------------------------------------------------|

| XRA     | TR<br>M | Logical XOR register or memory with<br>accumulator |

- The contents of the accumulator are XORed with the contents of the register or memory.

- The result is placed in the accumulator.

- If the operand is a memory location, its address is specified by the contents of H-L pair.

- S. Z. P are modified to reflect the result of the operation.

- CY and AC are reset.

- Example: XRA B or XRA M.

| Opcode | Operand    | Description                    |

|--------|------------|--------------------------------|

| XRI    | 8-bit data | XOR immediate with accumulator |

- The contents of the accumulator are XORed with the 8-bit data.

- The result is placed in the accumulator.

- S, Z, P are modified to reflect the result.

- CY and AC are reset.

- Example: XRI 86H.

| Opcode | Operand | Description                           |

|--------|---------|---------------------------------------|

| RAL    | None    | Rotate accumulator left through carry |

- Each binary bit of the accumulator is rotated left by one position through the Carry flag.

- Bit D7 is placed in the Carry flag, and the Carry flag is placed in the least significant position Do.

- CY is modified according to bit D7.

- S, Z, P, AC are not affected.

- Example: RAL.

| Opcode | Operand | Description                            |

|--------|---------|----------------------------------------|

| RAR    | None    | Rotate accumulator right through carry |

- Each binary bit of the accumulator is rotated right by one position through the Carry flag.

- Bit Do is placed in the Carry flag, and the Carry flag is placed in the most significant position D7.

- CY is modified according to bit Do.

- S, Z, P, AC are not affected.

- Example: RAR.

#### circular Left shift

| Opcode | Operand | Description             |

|--------|---------|-------------------------|

| RLC    | None    | Rotate accumulator left |

- Each binary bit of the accumulator is rotated left by one position.

- Bit D7 is placed in the position of Do as well as in the Carry flag.

- CY is modified according to bit D7.

- S, Z, P, AC are not affected.

- Example: RLC.

#### circular right shift

| Opcode | Operand | Description              |

|--------|---------|--------------------------|

| RRC    | None    | Rotate accumulator right |

- Each binary bit of the accumulator is rotated right by one position.

- Bit Do is placed in the position of D7 as well as in the Carry flag.

- CY is modified according to bit Do.

- S, Z, P, AC are not affected.

- Example: RRC.

| Opcode | Operand | Description            |

|--------|---------|------------------------|

| СМА    | None    | Complement accumulator |

The contents of the accumulator are complemented.

No flags are affected.

Example: CMA.

| Opcode    | Operand         | Description      |

|-----------|-----------------|------------------|

| СМС       | None            | Complement carry |

| • The Car | rry flag is con | nlomontod        |

- No other flags are affected.

- Example: CMC.

| Opendi<br>STC | - Operani<br>None | d Description<br>Set carry |

|---------------|-------------------|----------------------------|

|               |                   |                            |

| * The C       | arry flag is s    | iet to 1.                  |

| • No ot       | her flågs are     | affected.                  |

| • Exam        | ple: STC.         |                            |

| Ladi          | ipier in e.       |                            |

|               |                   |                            |

|               |                   |                            |

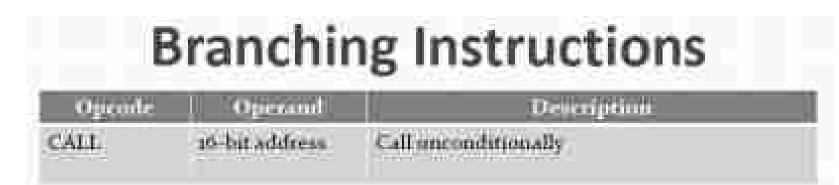

The branching instruction alter the normal sequential flow.

These instructions alter either unconditionally or conditionally.

| Opcode | Operand        | Description          |  |

|--------|----------------|----------------------|--|

| JMP    | 16-bit address | Jump unconditionally |  |

- The program sequence is transferred to the memory location specified by the 16-bit address given in the operand.

- Example: JMP 2034 H.

| Opcode | Operand        | Description        |

|--------|----------------|--------------------|

| Jx     | 16-bit address | Jump conditionally |

- The program sequence is transferred to the memory location specified by the 16-bit address given in the operand based on the specified flag of the PSW.

- **Example:** JZ 2034 H.

### Jump Conditionally

| Opcode | Description          | Status Flags              |

|--------|----------------------|---------------------------|

| JC.    | Jump if Carry        | CT-1                      |

| INC    | Jump if No Carry     | $C\dot{Y} = 0$            |

| 1P     | Jump if Positive     | S-0                       |

| JM     | Jump if Minus        | S – 1                     |

| jz.    | Jump if Zero         | Z=t                       |

| JNZ    | Jump if No Zero      | Z = 0                     |

| JPE    | Jump if Parity Even  | $\mathbf{P} = \mathbf{v}$ |

| JPO    | Jonns if Parity Odd. | $\mathbf{F} = \mathbf{Q}$ |

- The program sequence is transferred to the memory location specified by the 16-bit address given in the operand.

- Before the transfer, the address of the next instruction after CALL (the contents of the program counter) is pushed onto the stack.

- Example: CALL 2034 H.

| Opcode | Operand | Description            |

|--------|---------|------------------------|

| RET    | None    | Return unconditionally |

- The program sequence is transferred from the subroutine to the calling program.

- The two bytes from the top of the stack are copied into the program counter, and program execution begins at the new address.

- Example: RET.

| Opcode | Operand | Description  |

|--------|---------|--------------|

| NOP    | None    | No operation |

- No operation is performed.

- The instruction is fetched and decoded but no operation is executed.

- Example: NOP

| Opcode | Operand | Description |

|--------|---------|-------------|

| HEF    | None    | Halt        |

- The CPU finishes executing the current instruction and halts any further execution.

- An interrupt or reset is necessary to exit from the halt state.

- Example: HLT

| Opcode | Operand | Description       |

|--------|---------|-------------------|

| DI     | None    | Disable interrupt |

- The interrupt enable flip-flop is reset and all the interrupts except the TRAP are disabled.

- No flags are affected.

- Example: DI

| Opcode | Operand | Description      |

|--------|---------|------------------|

| EI     | None    | Enable interrupt |

- The interrupt enable flip-flop is set and all interrupts are enabled.

- No flags are affected.

- This instruction is necessary to re-enable the interrupts (except TRAP).

- Example: EI

#### Summary – Data transfer

- MOV Move

- MVI Move Immediate

- LDA Load Accumulator Directly from Memory

- STA Store Accumulator Directly in Memory

- LHLD Load H & L Registers Directly from Memory

- SHLD Store H & L Registers Directly in Memory

#### Summary Data transfer

- An 'X' in the name of a data transfer instruction implies that it deals with a register pair (16-bits);

- LXI Load Register Pair with Immediate data

- LDAX Load Accumulator from Address in Register Pair

- STAX Store Accumulator in Address in Register Pair

- XCHG Exchange H & L with D & E

- XTHL Exchange Top of Stack with H & L

#### Summary - Arithmetic Group

- Add, Subtract, Increment / Decrement data in registers or memory.

- ADD Add to Accumulator

- ADI Add Immediate Data to Accumulator

- ADC Add to Accumulator Using Carry Flag

- ACI Add Immediate data to Accumulator Using Carry

- SUB Subtract from Accumulator

- SUI Subtract Immediate Data from Accumulator

- SBB Subtract from Accumulator Using Borrow (Carry) Flag

- SBI Subtract Immediate from Accumulator Using Borrow (Carry) Flag

- INR Increment Specified Byte by One

- DCR Decrement Specified Byte by One

- INX Increment Register Pair by One

- DCX Decrement Register Pair by One

- DAD Double Register Add; Add Content of Register Pair to H & L Register Pair

### Summary Logical Group

- This group performs logical (Boolean) operations on data in registers and memory and on condition flags.

- These instructions enable you to set specific bits in the accumulator ON or OFF.

- ANA Logical AND with Accumulator

- ANI Logical AND with Accumulator Using Immediate Data

- ORA Logical OR with Accumulator

- OR Logical OR with Accumulator Using Immediate Data

- XRA Exclusive Logical OR with Accumulator

- XRI Exclusive OR Using Immediate Data

- The Compare instructions compare the content of an 8-bit value with the contents of the accumulator;

- CMP Compare

- CPI Compare Using Immediate Data

- The rotate instructions shift the contents of the accumulator one bit position to the left or right:

- RLC Rotate Accumulator Left

- RRC Rotate Accumulator Right

- RAL Rotate Left Through Carry

- RAR Rotate Right Through Carry

- Complement and carry flag instructions:

- CMA Complement Accumulator

- CMC Complement Carry Flag

- STC Set Carry Flag

#### Summary - Branch Group

#### Unconditional branching

- JMP Jump

- CALL Call

- RET Return

#### Conditions

NZ Not Zero (Z = 0)

Z Zero (Z = 1)

• NC No Carry (C =

$$0$$

)

$$\Box C \qquad Carry (C = 1)$$

$$\square PO \qquad Parity Odd (P = 0)$$

- PE Parity Even (P = 1)

- □ P Plus (S = 0)

- □ M Minus (S = 1)

- Conditional branching

#### Summary - Stack

- PUSH Push Two bytes of Data onto the Stack

- POP Pop Two Bytes of Data off the Stack

- XTHL Exchange Top of Stack with H & L

- SPHL Move content of H & L to Stack Pointer

#### I/0 instructions

# IN Initiate Input OperationOUT Initiate Output Operation

#### Summary - Machine Control instructions

- EI Enable Interrupt System

- DI Disable Interrupt System

- HLT Halt

- NOP No Operation

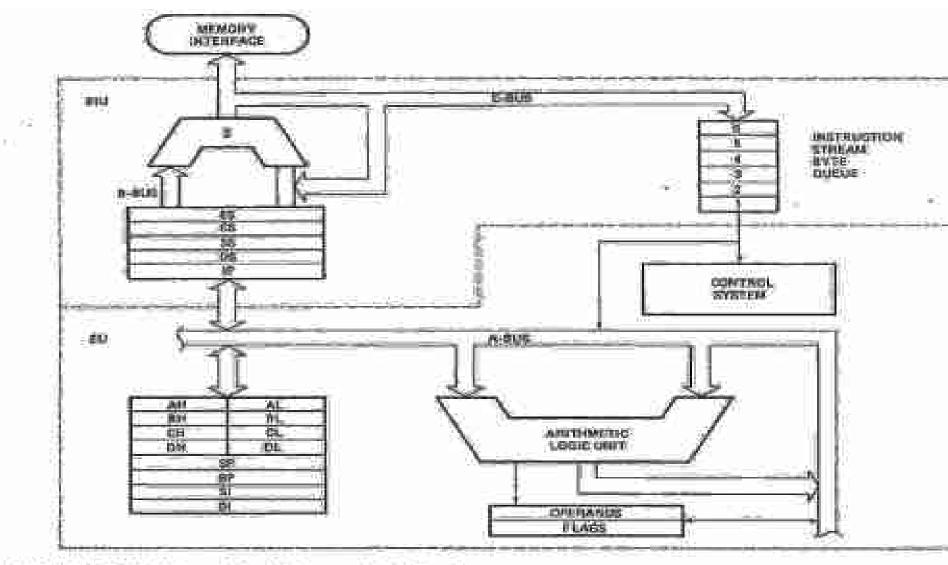

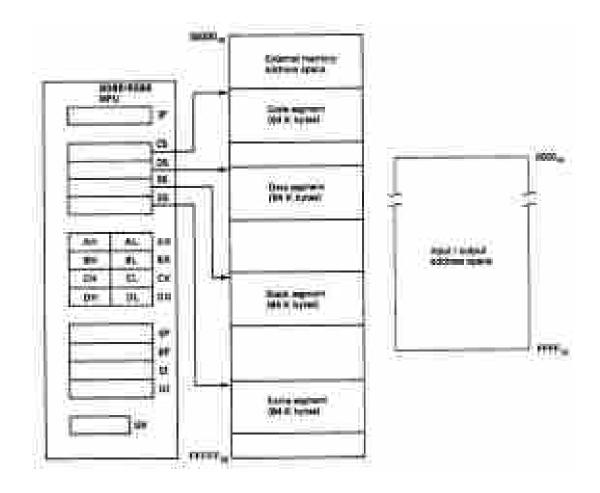

#### 8086 MICROPROCESSOR

#### Block diagram of 8086

FKAUKE 2-7 8086 (atomal block diagram. (Intel Corp.)

#### Software Model of the 8086 Microprocessors

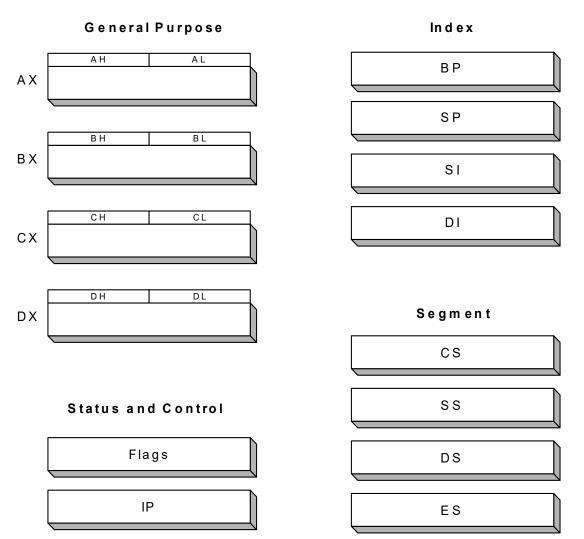

### 8086 Registers

## **General Purpose Registers**

| 15 <sup>H</sup> 8                            | 7 <sup>L</sup> 0 |  |  |  |  |  |  |

|----------------------------------------------|------------------|--|--|--|--|--|--|

| AX (Accu                                     | AX (Accumulator) |  |  |  |  |  |  |

| AH AL                                        |                  |  |  |  |  |  |  |

| BX (Base Register)                           |                  |  |  |  |  |  |  |

| BH BL                                        |                  |  |  |  |  |  |  |

| CX (Used as a counter)                       |                  |  |  |  |  |  |  |

| CH CL                                        |                  |  |  |  |  |  |  |

| DX (Used to point to data in I/O operations) |                  |  |  |  |  |  |  |

| DH DL                                        |                  |  |  |  |  |  |  |

AX - the Accumulator BX - the Base Register CX - the Count Register DX - the Data Register

- Normally used for storing temporary results

- Each of the registers is 16 bits wide (AX, BX, CX, DX)

- Can be accessed as either 16 or 8 bits AX, AH, AL

## **General Purpose Registers**

- AX

- Accumulator Register

- Preferred register to use in arithmetic, logic and data transfer instructions because it generates the shortest Machine Language Code

- Must be used in multiplication and division operations

- Must also be used in I/O operations

- **BX**

- Base Register

- Also serves as an address register

## **General Purpose Registers**

- CX

- Count register

- Used as a loop counter

- Used in shift and rotate operations

- DX

- Data register

- Used in multiplication and division

- Also used in I/O operations

## Pointer and Index Registers

| SP | Stack Pointer       |

|----|---------------------|

| BP | Base Pointer        |

| SI | Source Index        |

| DI | Destination Index   |

| IP | Instruction Pointer |

- All 16 bits wide, L/H bytes are not accessible

- Used as memory pointers

- Example: MOV AH, [SI]

- Move the byte stored in memory location whose address is contained in register SI to register AH

- IP is not under direct control of the programmer

## Flag Register

## 8086 Programmer's Model

BIU registers (20 bit adder)

| ES | E |

|----|---|

| CS | С |

| SS | S |

| DS | D |

| IP | h |

|    |   |

Extra Segment Code Segment Stack Segment Data Segment Instruction Pointer

#### **EU registers**

| AX | AH  | AL  |  |  |  |  |  |

|----|-----|-----|--|--|--|--|--|

| BX | BH  | BL  |  |  |  |  |  |

| СХ | СН  | CL  |  |  |  |  |  |

| DX | DH  | DL  |  |  |  |  |  |

|    | SP  |     |  |  |  |  |  |

|    | BP  |     |  |  |  |  |  |

|    | SI  |     |  |  |  |  |  |

|    | DI  |     |  |  |  |  |  |

|    | FLA | IGS |  |  |  |  |  |

|    |     |     |  |  |  |  |  |

Accumulator Base Register Count Register Data Register Stack Pointer Base Pointer Source Index Register Destination Index Register

## The Stack

- The stack is used for temporary storage of information such as data or addresses.

- When a CALL is executed, the 8086 automatically PUSHes the current value of CS and IP onto the stack.

- Other registers can also be pushed

- Before return from the subroutine, POP instructions can be used to pop values back from the stack into the corresponding registers.

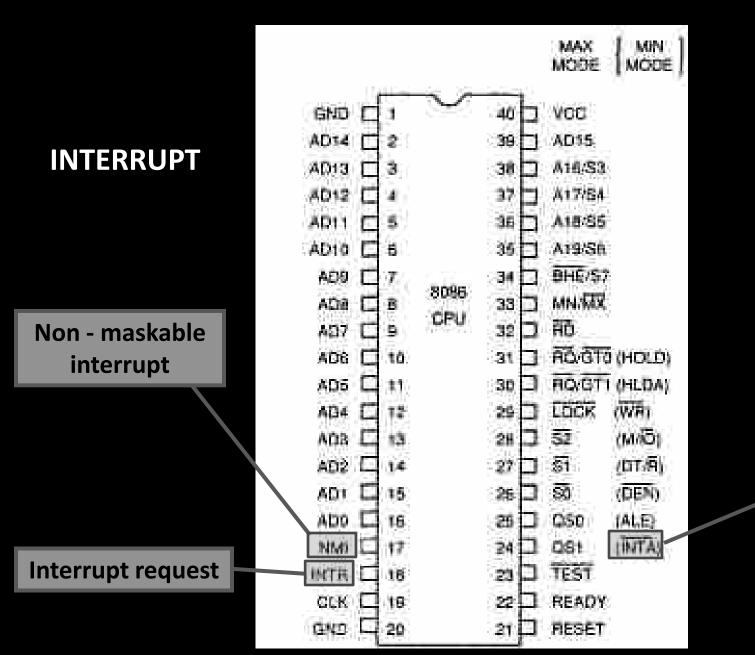

15

Interrupt acknowledge

S6: Logic 0.

S5: Indicates condition of IF flag bits.

S4-S3: Indicate which segment is accessed during current bus cycle:

| \$4 53 | Frantin              |

|--------|----------------------|

| 1000   | Edm inguinat         |

| 500 1  | Stark segment        |

| 1.0    | Citize or no segment |

| t È ,  | Data segment         |

|       |                          |        |               |    | MAX<br>MODE | MODE      |

|-------|--------------------------|--------|---------------|----|-------------|-----------|

| GND   | d,                       | $\sim$ | 40            | Ь  | VCC         |           |

| AD14  | <b>C</b> 2               |        | 39            | Þ  | AD15        |           |

| AD13  | ЦЗ                       |        | 38            |    | A16/S3      |           |

| AD12  | E e                      |        | 37            |    | A17/84      |           |

| AD11  | C 5                      |        | 36            |    | A18/85      |           |

| AD10  | Ц в                      |        | 35            |    | A19/Sh      |           |

| AD9   | $\Box_{\mathcal{T}_{i}}$ | media: | 2 <b>3</b> 49 | þ, | BHE/\$7     |           |

| ADB   | БВ                       | 8086   | 33            |    | MN/MX       |           |

| A07   | <b>D</b> 9               | CPU    | 32            |    | AD.         |           |

| ADG   | 10                       |        | 31            |    | AD/GTC      | (HOLD)    |

| AD5   | É.M.                     |        | 30            |    | RO/GTI      | (HEDA)    |

| AD4   | 12                       |        | 29            |    | ECCR        | (978)     |

| ADB . | C 13                     |        | 28            | 3  | 52          | (M/10)    |

| AD2   | 14                       |        | 27            |    | ST .        | (bt/9)    |

| A01   | E (15)                   |        | 25            |    | 50          | (DEN)     |

| AD0   | 16                       |        | 26            |    | QS0         | (ALE)     |

| N540  | 017                      |        | 24            | Þ  | 081         | INTAS     |

| INTR- | 16                       |        | 23            | Þ  | TEST        | 110204060 |

| CCK   | 18                       |        | 22            | Þ  | READY       |           |

| GND   | 20                       |        | 21            | þ  | RESET       |           |

Address/Status Bus Address bits A<sub>19</sub> –

A<sub>16</sub> & Status bits S<sub>6</sub>

$-S_3$

BHE#, A<sub>0</sub>:

**0,0:** Whole word (16-bits)

**0,1:** High byte to/from odd address

**1,0:** Low byte to/from even address

1,1: No selection

|        |           |        |      |    | MAX         | MON      |

|--------|-----------|--------|------|----|-------------|----------|

| GND [  | (T        | $\sim$ | -40  | b  | VCC         |          |

| AD14   | \$        |        | 39   | b  | AD15        |          |

| ADIA 🗖 | 3         |        | 38   | b, | A16/S3      |          |

| AD12 C |           |        | 37   |    | A17/64      |          |

| AD11   | 5         |        | 36   |    | A18/85      |          |

| ADIO C | 16 C      |        | 35   | Ð, | A19/Sh      | _        |

| AD9 E  | $\pi_{i}$ |        | 2348 |    | BHE/S7      | <u> </u> |

| ADA D  | в         | 8086   | 33   |    | MNIN        |          |

| A07 E  | 9         | CPU    | 32   | D. | ĀĐ          |          |

| AD6 C  | 10        |        | 31   |    | AD/GTO      | (HOLD)   |

| AD5 C  | 3870      |        | 30   |    | ROUGTI      | (HLDA)   |

| AD4 E  | 12        |        | 29   |    | ECCR        | (WR)     |

| ADB E  | 13        |        | 28   | 3  | 52          | (MAG)    |

| AD2 🗔  | 14        |        | 27   | b  | <b>\$</b> 1 | (DT/A)   |

| AD1 E  | (15)      |        | 25   |    | <u>80</u>   | (DEN)    |

| ADO E  | 16        |        | 26   |    | QS0         | (ALE)    |

| NEAD E | 17        |        | 24   |    | QSt         | INTAS    |

| INTR E | 18        |        | 23   | D  | TEST        | AC060    |

| CLK [  | 18        |        | 22   | Þ  | READY       |          |

| ans C  | 20        |        | 21   | þ  | RESET       |          |

### **Bus High Enable/S7**

Enables most significant data bits  $D_{15} - D_8$  during read or write operation.

S<sub>7</sub>: Always 1.

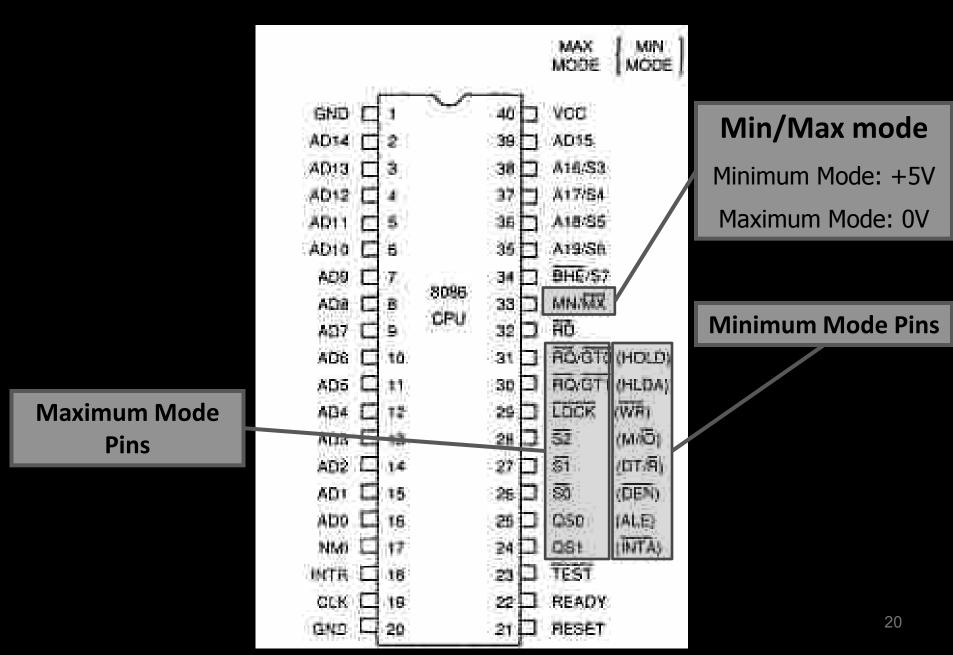

### **Minimum Mode- Pin Details**

### **Maximum Mode - Pin Details**

### S2 S1 S0

000: INTA 001: read I/O port 010: write I/O port 011: halt 100: code access 101: read memory 110: write memory 111: none -passive

| ð   | $\sim$                      | 40                                                                                                                                               | 3                                                                                                                                                            | VCC                                                                                                                                                                 |

|-----|-----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2   |                             | 39                                                                                                                                               | 3                                                                                                                                                            | AD15                                                                                                                                                                |

| 3   |                             | 36                                                                                                                                               | 3                                                                                                                                                            | A16/S3                                                                                                                                                              |

| 4   |                             | 37                                                                                                                                               | 3                                                                                                                                                            | A17/S4                                                                                                                                                              |

| 5   |                             | 36                                                                                                                                               | Ď,                                                                                                                                                           | A18/S5                                                                                                                                                              |

| 5   |                             | 35                                                                                                                                               | 1                                                                                                                                                            | A19/S8                                                                                                                                                              |

| 2   | (100) (100)                 | 34                                                                                                                                               | 3                                                                                                                                                            | BHE/S7                                                                                                                                                              |

| 8   | 101000                      | 33                                                                                                                                               | 3                                                                                                                                                            | MNMX                                                                                                                                                                |

| 9   | CPU                         | 32                                                                                                                                               |                                                                                                                                                              | ĦĎ                                                                                                                                                                  |

| 10  |                             | 31                                                                                                                                               | 1                                                                                                                                                            | RO/GTO                                                                                                                                                              |

| 11  |                             | 30 İ                                                                                                                                             | 1                                                                                                                                                            | RC/GT1                                                                                                                                                              |

| 12: |                             | 29                                                                                                                                               |                                                                                                                                                              | LOCK                                                                                                                                                                |

| 13  |                             | 28                                                                                                                                               |                                                                                                                                                              | 52                                                                                                                                                                  |

| 14  |                             | 27                                                                                                                                               | 3                                                                                                                                                            | 51                                                                                                                                                                  |

| 15  |                             | 26                                                                                                                                               | 3                                                                                                                                                            | SO                                                                                                                                                                  |

| 16  |                             | 25                                                                                                                                               | 2                                                                                                                                                            | QSO                                                                                                                                                                 |

| 17  |                             | 24                                                                                                                                               | 3                                                                                                                                                            | Q\$1                                                                                                                                                                |

| 18  |                             | 23                                                                                                                                               | 3                                                                                                                                                            | TEST                                                                                                                                                                |

| 19  |                             | 22                                                                                                                                               | 1                                                                                                                                                            | READY                                                                                                                                                               |

| 20  |                             | 21                                                                                                                                               | 1                                                                                                                                                            | RESET                                                                                                                                                               |

|     | 234567891011213141516171819 | 2<br>3<br>4<br>5<br>6<br>7<br>8<br>6<br>7<br>8<br>6<br>7<br>8<br>055<br>8<br>9<br>10<br>11<br>12<br>13<br>14<br>15<br>16<br>17<br>16<br>17<br>16 | 2 39<br>3 36<br>4 37<br>5 36<br>6 35<br>7 8085 33<br>9 32<br>10 31<br>11 30<br>12 29<br>13 28<br>14 27<br>15 26<br>16 25<br>17 24<br>16 25<br>17 24<br>18 23 | 2 39 37<br>3 35 37<br>4 36 37<br>5 6 35 35 35<br>7 8055 35 37<br>9 10 31 30 7<br>9 10 11 29 7<br>10 11 29 7<br>11 29 7<br>13 28 7<br>14 25 7<br>16 17 23 7<br>19 22 |

### **Status Signal**

Inputs to 8288 to generate eliminated signals due to max mode.

### **Maximum Mode - Pin Details**

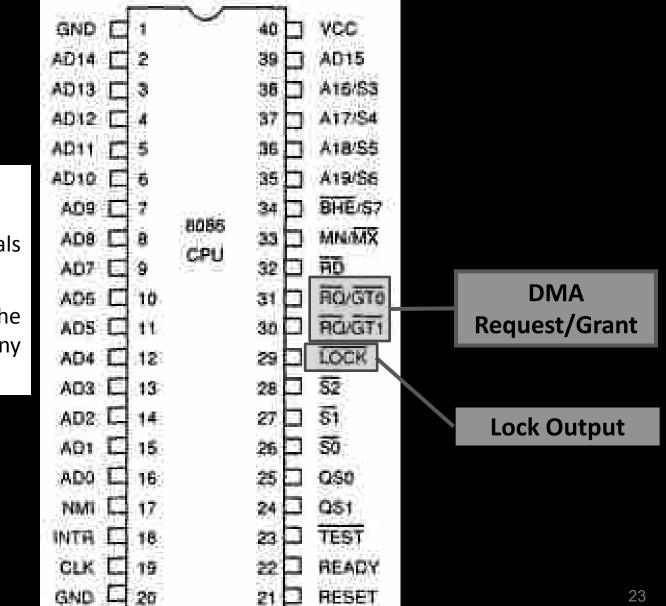

### Lock Output

Used to lock peripherals off the system

Activated by using the LOCK: prefix on any

instruction

### **Maximum Mode - Pin Details**

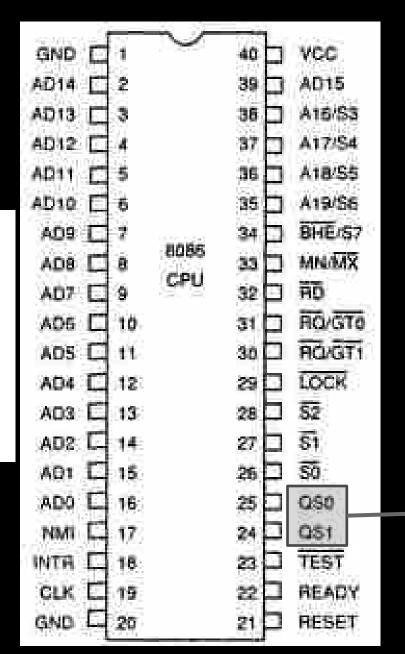

### QS1 QS0

- 00: Queue is idle

- 01: First byte of opcode

- 10: Queue is empty

- 11: Subsequent byte of opcode

### **Queue Status**

Used by numeric coprocessor (8087)

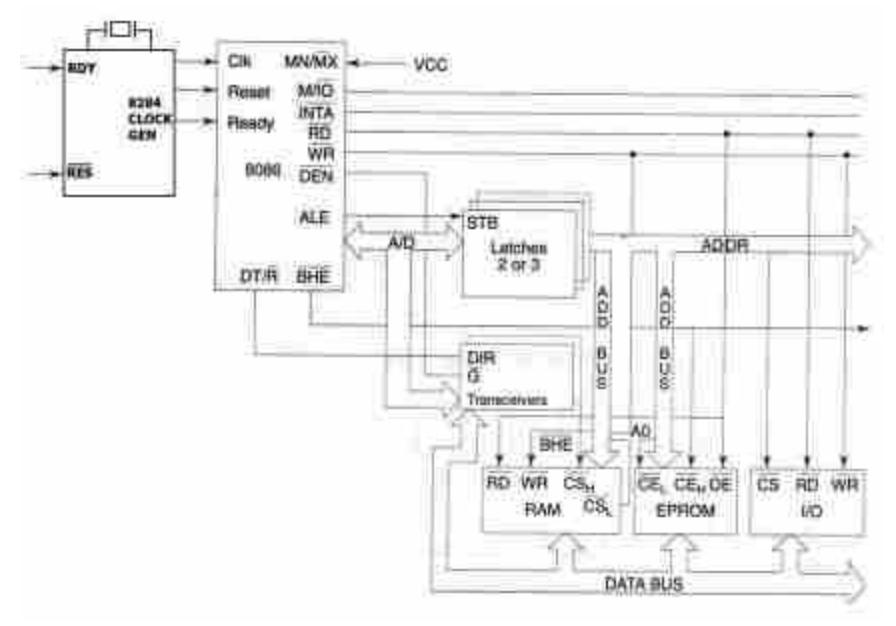

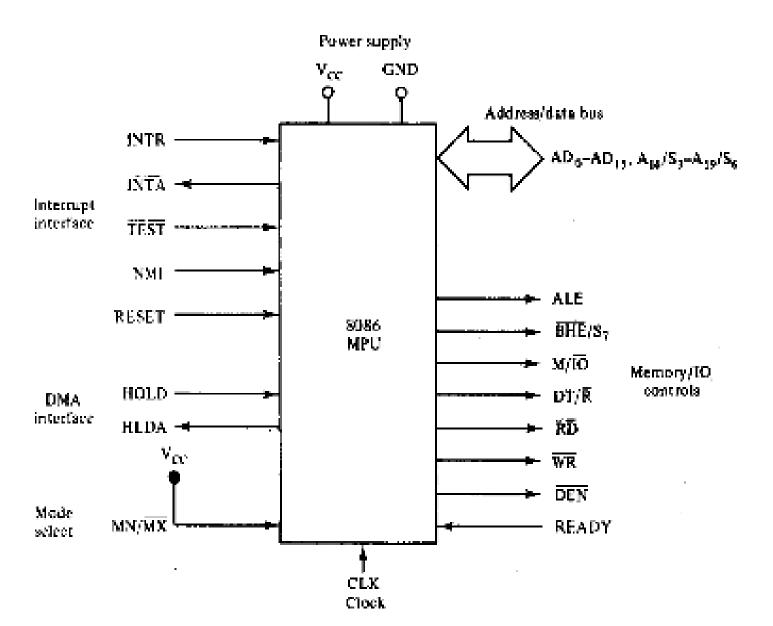

### Minimum Mode 8086 System

### Minimum Mode 8086 System

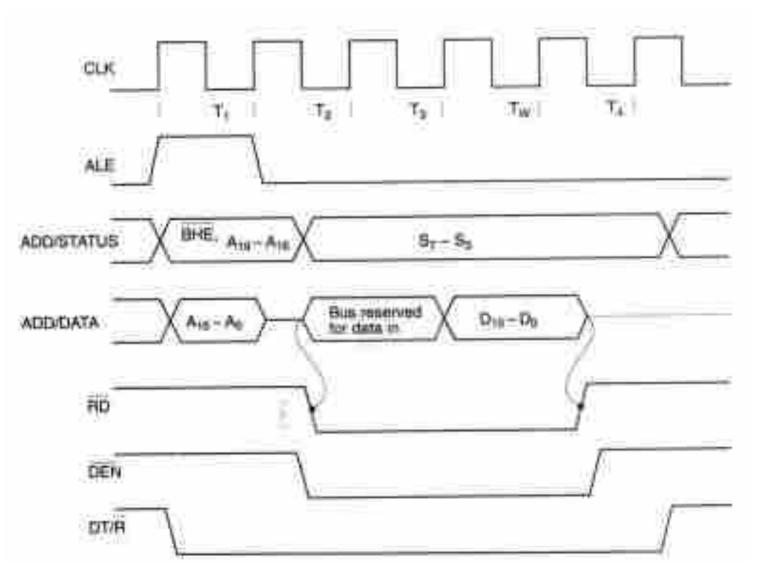

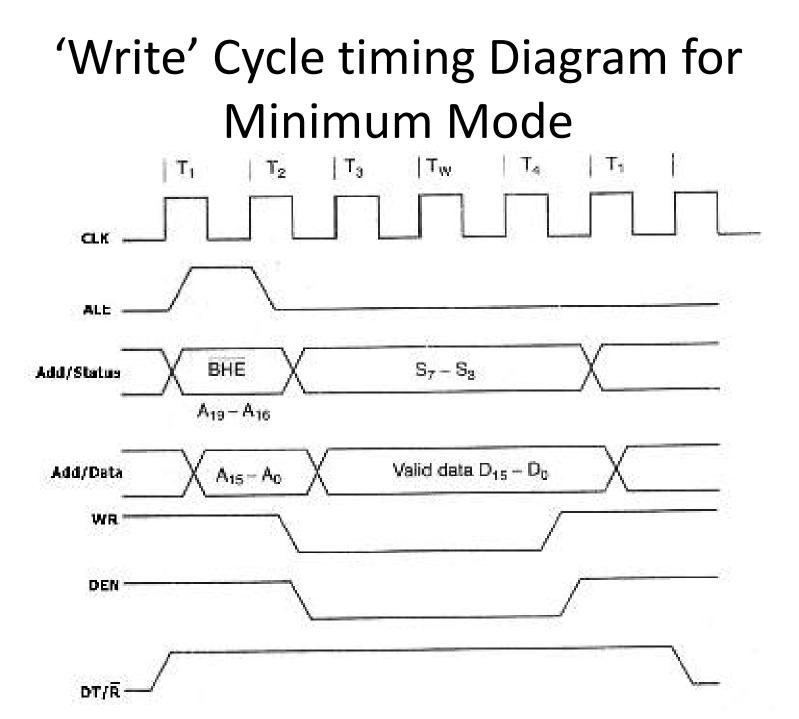

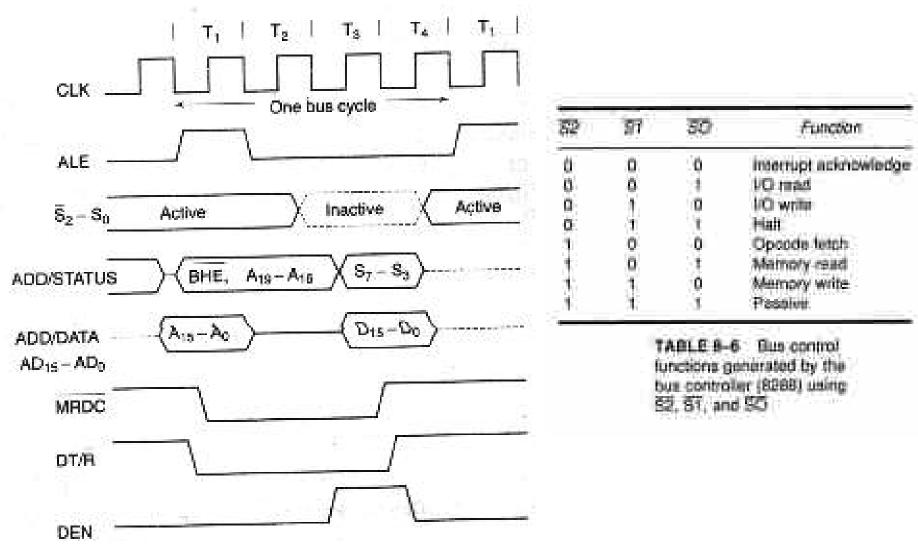

### 'Read' Cycle timing Diagram for Minimum Mode

27

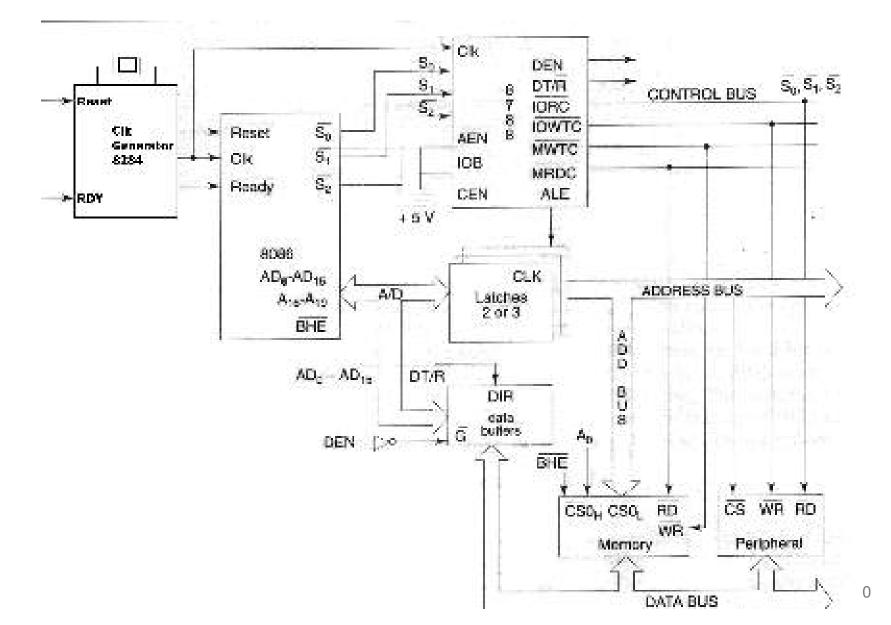

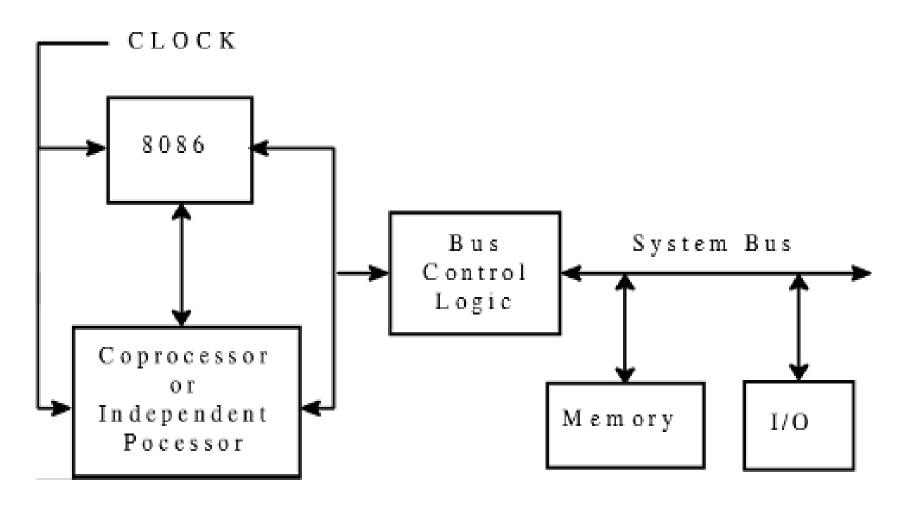

### Maximum Mode 8086 System

### Maximum Mode 8086 System

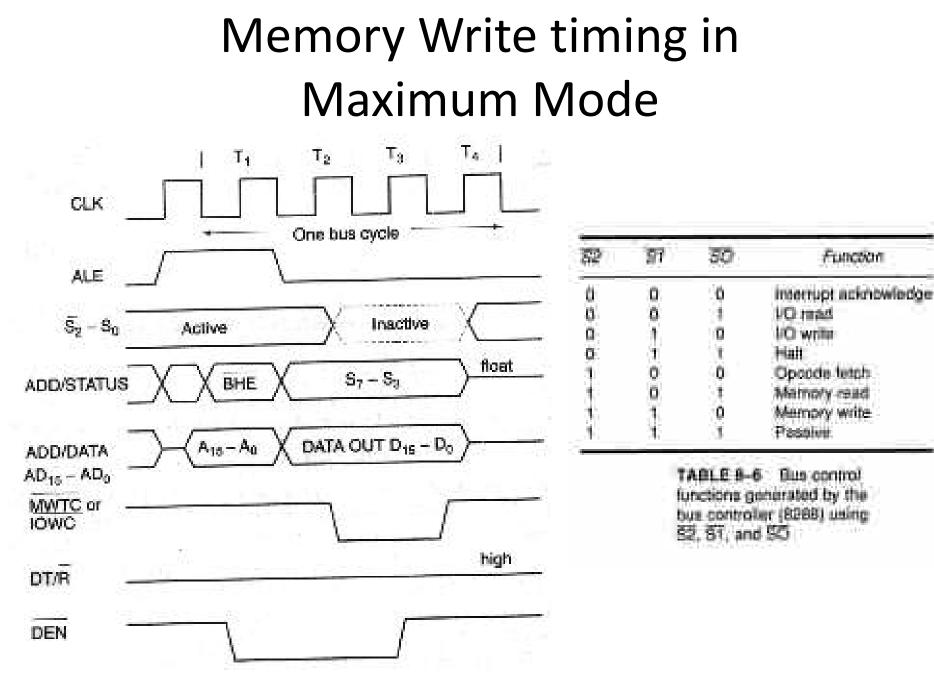

## Maximum Mode 8086 System

- Here, either a numeric coprocessor of the type 8087 or another processor is interfaced with 8086.

- The Memory, Address Bus, Data Buses are shared resources between the two processors.

- The control signals for Maximum mode of operation are generated by the Bus Controller chip 8788.

- The three status outputs S0\*, S1\*, S2\* from the processor are input to 8788.

- The outputs of the bus controller are the Control Signals, namely DEN, DT/R\*, IORC\*, IOWTC\*, MWTC\*, MRDC\*, ALE etc.

## Memory Read timing in Maximum Mode

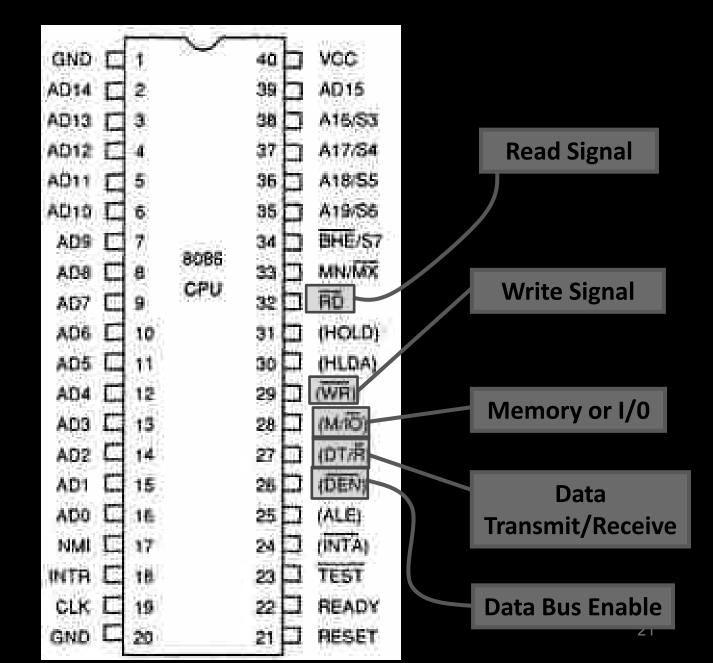

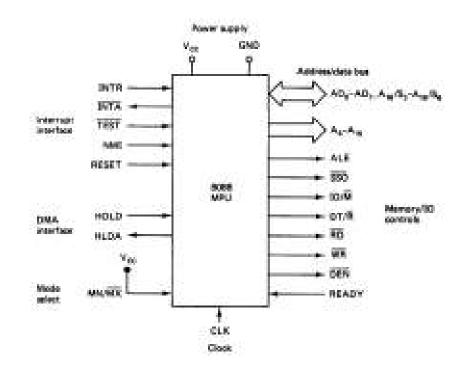

## 8086 Control Signals

- **1. ALE**

- **2. BHE**

- 3. M/IO

- 4. DT/R

- 5. RD

- 6. WR

- **7. DEN**

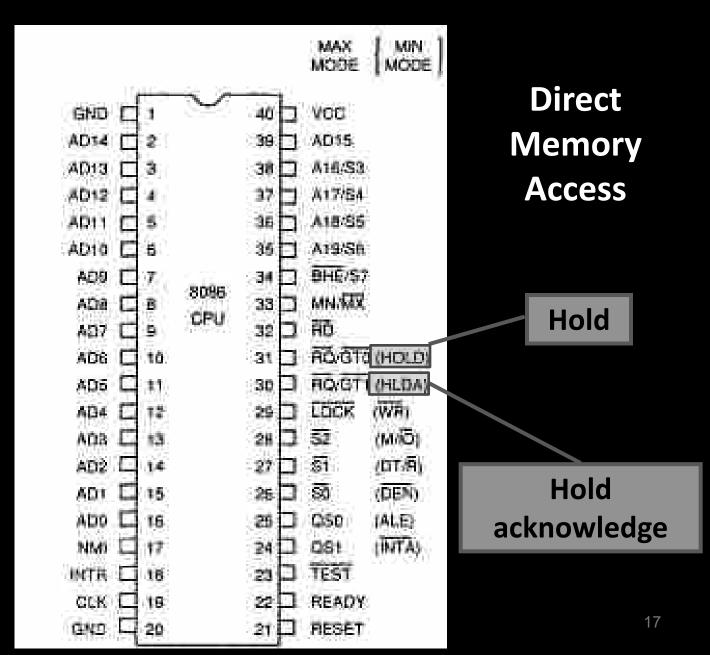

- Multiprocessor Systems refer to the use of multiple processors that executes instructions simultaneously and communicate with each other using mail boxes and Semaphores.

- Maximum mode of 8086 is designed to implement 3 basic multiprocessor configurations:

- 1. Coprocessor (8087)

- 2. Closely coupled (8089)

- 3. Loosely coupled (Multibus)